# Development of Advanced Pixel Detectors for X-ray Astronomy with SOI Technology

Ayaki Takeda

# DOCTOR OF PHILOSOPHY

Department of Particle and Nuclear Physics, School of High Energy Accelerator Science, The Graduate University for Advanced Studies

2014

# Abstract

X-ray astronomy is the one of the important research fields to understand the universe. The first X-ray detection in the universes other than the Sun was observed with the rocket by B.Rossi and R.Giacconi in 1962. X-ray astronomy has grown quickly since then.

As of 2013, three X-ray astronomical satellites, Suzaku, X-ray Multi-Mirror Mission (XMM-Newton), and Chandra, are operated in the space. The standard imaging spectrometers of these modern X-ray astronomical satellites are X-ray Charge Coupled Device's (CCD). The X-ray CCD offers Fano limited X-ray spectroscopic performance with the readout noise of about 3 electrons. It allows us to do wide and fine imaging with the sensor size of 20 - 30 mm square and a pixel size of  $\sim 30 \ \mu$ m. However, it has some weakness. The most serious issue is a non-X-ray background (NXB) generated by high energy particles on orbit. Especially it has serious influence above 10 keV. The rate of the NXB is too high to study faint sources. Therefore, a low background detector is desired in the next generation. Moreover, time resolution is too poor to make fast timing study of time variable sources (e.g., millisecond pulsar).

Future X-ray astronomical satellite missions will require a new type of detectors that can distinguish X-rays and charged particle tracks, so as to reduce the background level. The new detector must have good coincidence time resolution (~ 1  $\mu$ s), superior hit-position readout time (~ 10  $\mu$ s) in order to reduce the NXB by cosmic rays. By introducing an anti-coincidence method between the hit signal and the external active shield detector, the background produced by the cosmic ray tracks can be greatly reduced. This is particularly important for the observation of hard X-rays with energies above 10 keV. In addition, it must have wide bandpass (from soft to hard X-rays, 0.3 – 40 keV), and comparable performance in terms of imaging spectroscopy.

In order to realize the detector described above, we have been developing a new type of active pixel sensor (APS) called XRPIX based on the semiconductor pixel detector with the silicon-on-insulator (SOI) complementary metal-oxide semiconductor (CMOS) technology. This new technology, i.e., SOI pixel detector (SOIPIX), has been developed by High Energy Accelerator Research Organization (KEK) in recent years. Thereby, we designed "Event-Driven SOIPIX" with a trigger information output function as "XRPIX series". And we realize the spectroscopy system which reduce background rate of the NXB by two orders of magnitude compared with the CCD. Finally, we aim to employ the XRPIX in the next generation X-ray astronomical satellite.

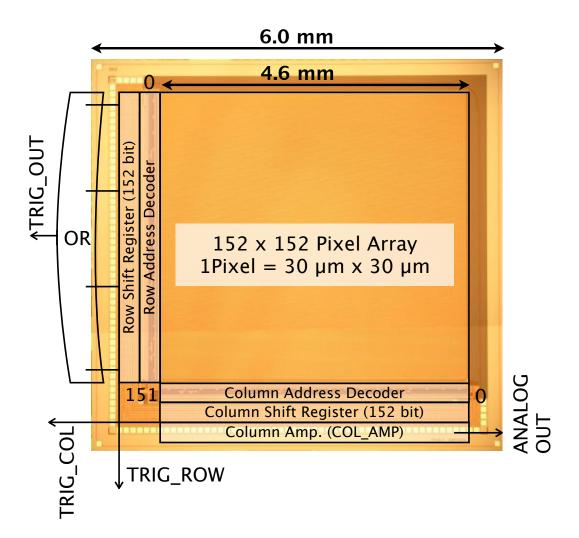

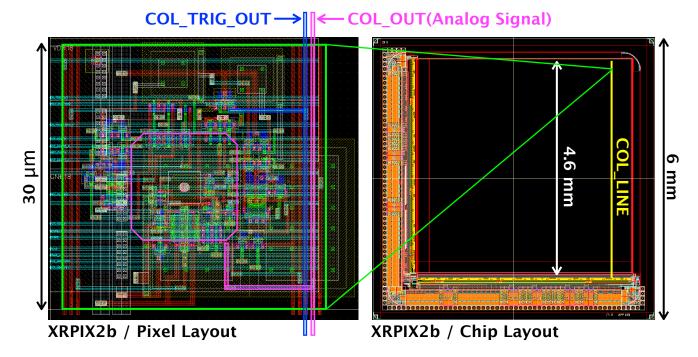

XRPIX series has designed six devices of XRPIX1/1b/2/2b/3/3b until now. In each chip, Event-Driven readout and spectroscopic performance are tested and improved. The XRPIX2b has a middle size of sensing area (effective area is 4.6 mm sq., pixel size is 30  $\mu$ m sq., number of pixels is 20 k) and succeeded in acquisition of the spectrum by Event-Driven readout mode. We think this is a world first detector realized this function. The event rate tolerance is over 1 kHz.

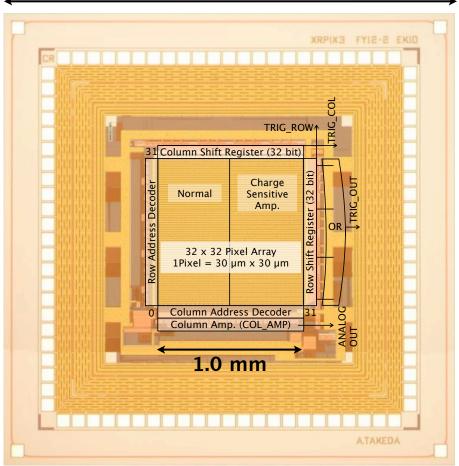

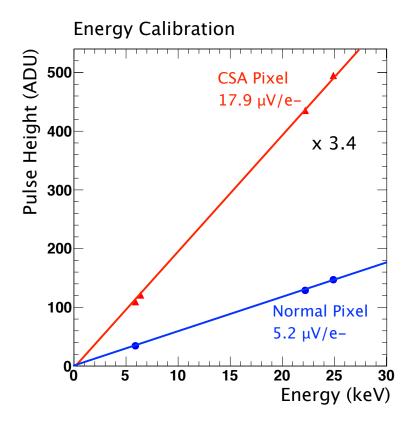

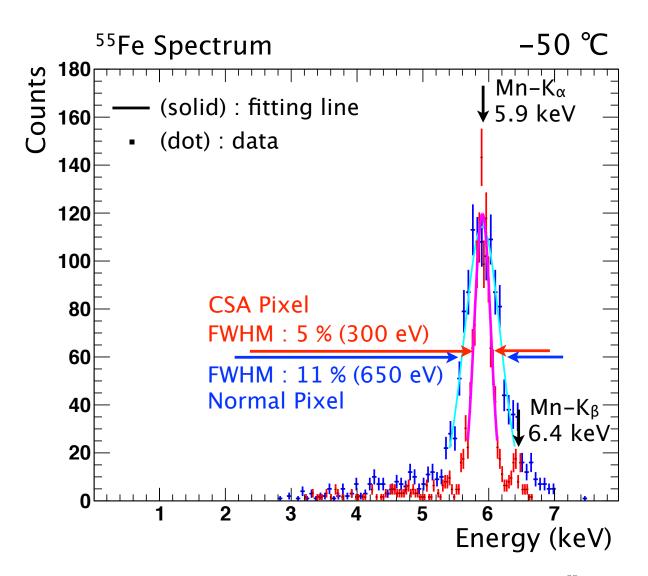

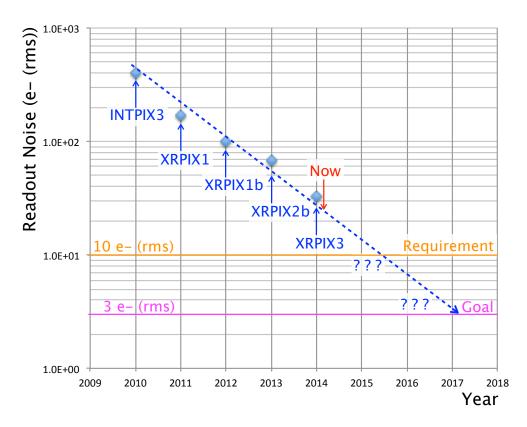

In view point of the spectroscopic performance, XRPIX3 achieved best performance in the SOIPIX detectors. It includes a charge sensitive amplifier in each pixel for the first time in the XRPIX series. The gain of X-ray responsivity is 17.9  $\mu$ V/e-. The readout noise is 33 electrons rms from the pedestal peak and the energy resolution is about 300 eV FWHM at 5.9 keV from <sup>55</sup>Fe radio isotope. Furthermore, XRPIX3 resolved Mn – K<sub> $\alpha$ </sub> (5.9 keV) and Mn – K<sub> $\beta$ </sub> (6.4 keV) successfully for the first time in our series. Thereby, XRPIX reached the spectroscopic performance accepted as an X-ray detector.

In this study, I have done many basic studies for the XRPIX by using device and circuit simulators. Then I have designed many prototype chips and measured performance of the chips with X-rays. In addition, I have done cooling test of the detector and analyzed the source of the leakage current etc. Through these work, I think I can demonstrate the possibility of the XRPIX for future X-ray astronomy satellite missions.

# Contents

| 1        | Intr | oducti  | on                                    | 1                   |

|----------|------|---------|---------------------------------------|---------------------|

| <b>2</b> | Rev  | riew of | Pixel Detector Technology             | 7                   |

|          | 2.1  |         | onductor Physics                      | 7                   |

|          |      | 2.1.1   | p-n Junction                          | 7                   |

|          |      | 2.1.2   | Depletion Region                      | 7                   |

|          | 2.2  | Radiat  | - 0                                   | 9                   |

|          |      | 2.2.1   | Photon Interactions                   | 9                   |

|          |      | 2.2.2   | Charged Particle Interactions         | 10                  |

|          |      | 2.2.3   | Fano Factor                           | 11                  |

|          | 2.3  | Analog  | g CMOS Circuit                        | 12                  |

|          |      | 2.3.1   | CMOS                                  | 12                  |

|          |      | 2.3.2   | Clock Feedthrough                     | 12                  |

|          |      | 2.3.3   | kT/C Noise                            | 13                  |

|          | 2.4  | Other   | Pixel Detector Technology             | 13                  |

|          |      | 2.4.1   | CCD                                   | 13                  |

|          |      | 2.4.2   | Medipix                               | 13                  |

|          |      | 2.4.3   | DEPFET                                | 14                  |

|          |      | 2.4.4   | PILATUS                               | 16                  |

|          |      | 2.4.5   | MIMOSA                                | 17                  |

| 3        | SOI  | Pixel   | Detector                              | 19                  |

|          | 3.1  |         | pment of SOI Pixel Detector           | 19                  |

|          | 3.2  |         | echnology                             | 20                  |

|          | 3.3  |         | s of SOI Wafer                        | 21                  |

|          |      | 3.3.1   | Czochralski Method                    | 21                  |

|          |      | 3.3.2   | Floating Zone Method                  | 22                  |

|          |      | 3.3.3   | Smart Cut <sup>TM</sup> Process       | 23                  |

|          |      | 3.3.4   | High Resistivity SOI Wafer for SOIPIX | $\overline{24}$     |

|          | 3.4  |         | ixel Process                          | $\overline{25}$     |

|          | 0.1  | 3.4.1   | Structure of SOIPIX                   | $\frac{-\circ}{25}$ |

|          |      | 3.4.2   | Buried P-Well                         | $27^{-5}$           |

|          |      | 3.4.3   | Circuit Layer                         | $\frac{-}{28}$      |

|          |      | 3.4.4   | Sensor Layer                          | $\frac{-0}{29}$     |

|          | 3.5  |         | Project Wafer Run                     | 30                  |

|          | 3.6  |         | pment of Advanced SOIPIX Technology   | 30                  |

|          | 0.0  | 3.6.1   | Stitching                             | 30                  |

|          |      |         | Double SOI Wafer                      | 30                  |

| <b>4</b> | Des | sign for X-ray Astronomy                                                                                      |   |  |   | <b>34</b> |

|----------|-----|---------------------------------------------------------------------------------------------------------------|---|--|---|-----------|

|          | 4.1 | Concept                                                                                                       |   |  |   | . 34      |

|          | 4.2 | XRPIX Series                                                                                                  |   |  |   | . 36      |

|          |     | 4.2.1 XRPIX Project                                                                                           |   |  |   | . 36      |

|          |     | 4.2.2 XRPIX1                                                                                                  |   |  |   | . 36      |

|          |     | 4.2.3 XRPIX1b                                                                                                 |   |  |   | . 38      |

|          |     | 4.2.4 XRPIX2                                                                                                  |   |  |   | . 38      |

|          |     | 4.2.5 XRPIX2b                                                                                                 |   |  |   | . 39      |

|          |     | 4.2.6 XRPIX3                                                                                                  |   |  |   | . 40      |

|          |     | 4.2.7 XRPIX3b                                                                                                 |   |  |   | . 41      |

|          |     | 4.2.8 Specification Summary of XRPIX Series                                                                   |   |  |   | . 41      |

|          | 4.3 | Design of XRPIX                                                                                               |   |  |   |           |

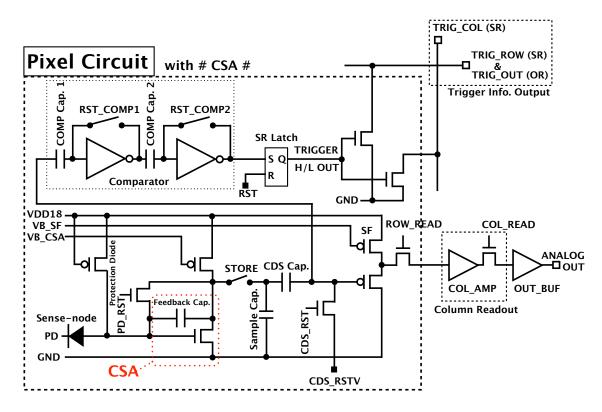

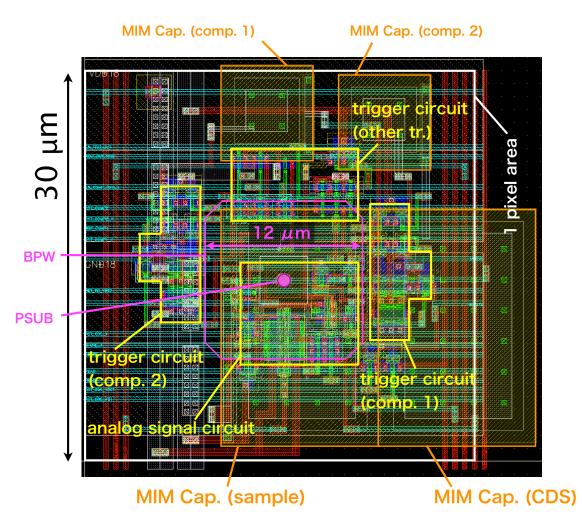

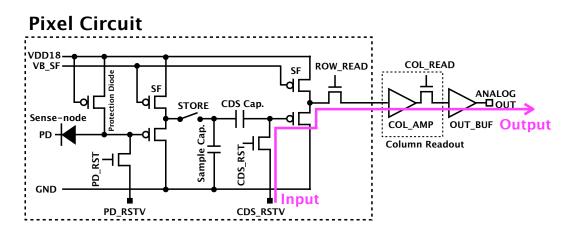

|          |     | 4.3.1 Pixel Circuit                                                                                           |   |  |   |           |

|          |     | 4.3.2 Peripheral Circuit                                                                                      |   |  |   |           |

|          | 4.4 | Operation Architecture                                                                                        |   |  |   |           |

|          |     | 4.4.1 Pixel Circuit                                                                                           |   |  |   |           |

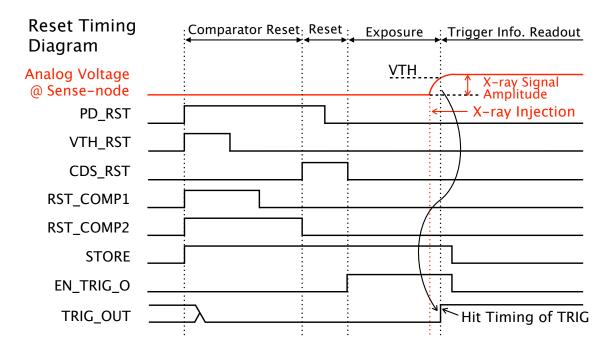

|          |     | 4.4.2 Trigger Circuit                                                                                         |   |  |   |           |

|          |     | 4.4.3 Bad Pixel Mask and Control Register Writing                                                             |   |  |   | -         |

|          | 4.5 | Data Acquisition System                                                                                       |   |  |   |           |

|          |     | 4.5.1 Hardware                                                                                                |   |  |   |           |

|          |     | 4.5.2 Software                                                                                                |   |  |   |           |

|          |     |                                                                                                               |   |  |   |           |

| <b>5</b> | Eva | aluation of XRPIX                                                                                             |   |  |   | 52        |

|          | 5.1 | Experiment Setup                                                                                              | • |  | • |           |

|          |     | 5.1.1 Setup of KEK $\ldots$  |   |  |   |           |

|          |     | 5.1.2 Setup of Kyoto University                                                                               | • |  | • | . 52      |

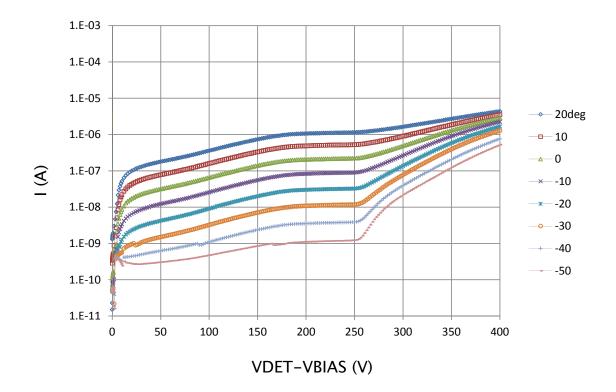

|          | 5.2 | Diode Characteristic                                                                                          |   |  |   | . 54      |

|          |     | 5.2.1 IV Measurements                                                                                         | • |  | • | . 54      |

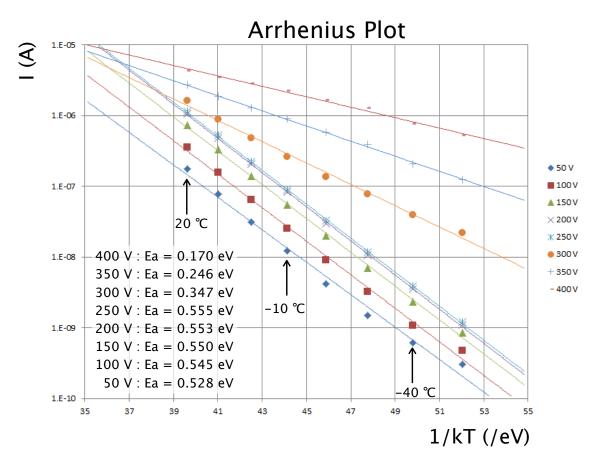

|          |     | 5.2.2 Arrhenius Plot                                                                                          |   |  |   | . 55      |

|          | 5.3 | CV Measurements                                                                                               |   |  |   |           |

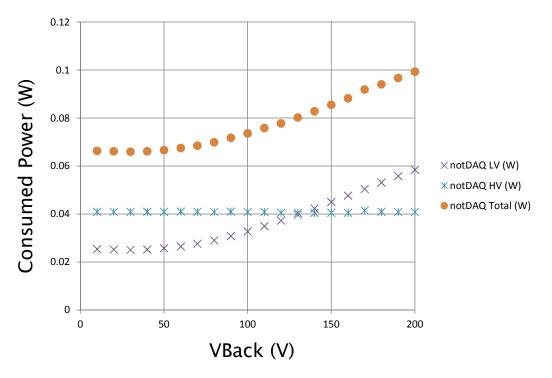

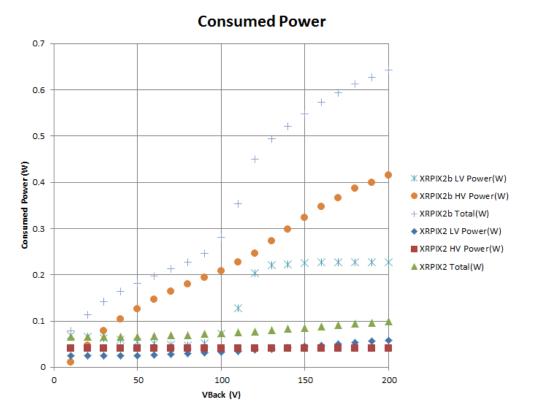

|          | 5.4 | Consumed Power                                                                                                |   |  |   |           |

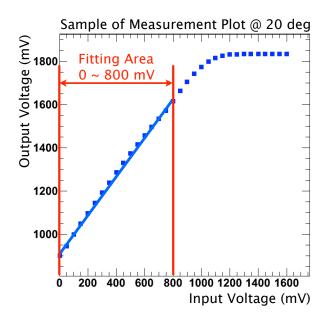

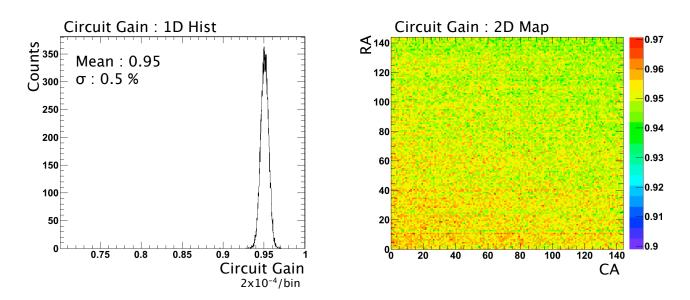

|          | 5.5 | Circuit Gain                                                                                                  |   |  |   | . 58      |

|          | 5.6 | XRPIX2b Operation                                                                                             |   |  |   |           |

|          |     | 5.6.1 Observing of Analog Waveform                                                                            | • |  |   | . 59      |

|          |     | 5.6.2 Output of Trigger Information                                                                           |   |  |   | . 62      |

|          |     | 5.6.3 Writing of Bad Pixel Mask and Control Register                                                          |   |  |   | . 63      |

|          | 5.7 | X-ray Responsivity                                                                                            |   |  |   | . 65      |

|          |     | 5.7.1 Analysis Method                                                                                         |   |  |   | . 65      |

|          |     | 5.7.2 X-ray Spectra $\ldots$ |   |  |   | . 66      |

|          |     | 5.7.3 Calibration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            |   |  |   | . 67      |

|          |     | 5.7.4 Improvement of Spectroscopic Performance                                                                |   |  |   | . 67      |

|          | 5.8 | Event-Driven X-ray Readout                                                                                    |   |  |   | . 71      |

|          |     | 5.8.1 X-ray Spectra                                                                                           |   |  |   | . 71      |

|          |     | 5.8.2 Calibration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            |   |  |   | . 72      |

|          |     | 5.8.3 Observing of Analog Signal                                                                              |   |  |   |           |

|          |     | 5.8.4 Spectra Shape of Frame and Event-Driven Readout                                                         |   |  |   | . 77      |

|          |     | 5.8.5 Energy Peak Shift by Changing a Threshold Voltage                                                       |   |  |   |           |

| 6            | Discussion |                                                         |    |  |  |  |

|--------------|------------|---------------------------------------------------------|----|--|--|--|

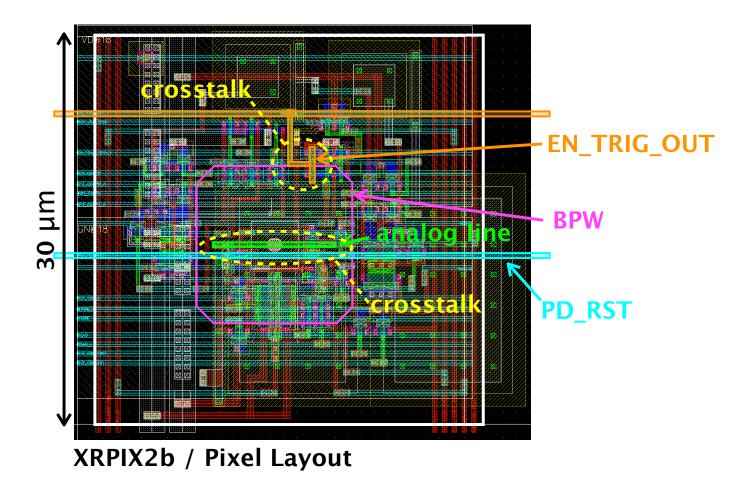

|              | 6.1        | Crosstalk of the Control Signal in the Layout           | 80 |  |  |  |

|              |            | 6.1.1 The Crosstalk in Reset Operation of Pixel Circuit | 80 |  |  |  |

|              |            | 6.1.2 The Crosstalk by Trigger Signal Conversion        | 81 |  |  |  |

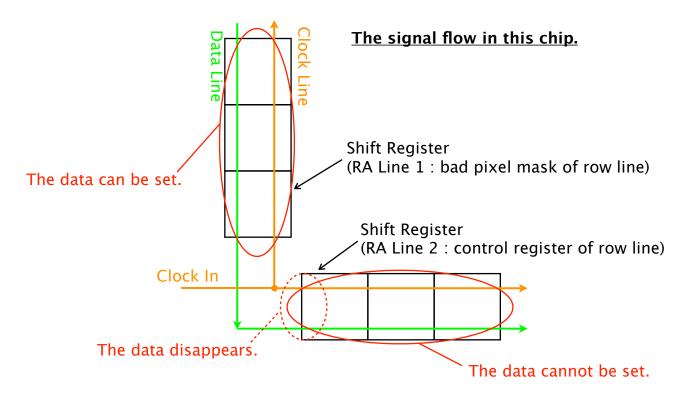

|              | 6.2        | "Clock Race" Problems                                   | 82 |  |  |  |

|              | 6.3        | Event-Driven Readout                                    | 83 |  |  |  |

|              | 6.4        | Spectroscopic Performance                               | 84 |  |  |  |

|              | 6.5        | Pixel Circuit                                           | 84 |  |  |  |

|              | 6.6        | Pixel Structure                                         | 85 |  |  |  |

| 7            | Con        | clusion                                                 | 86 |  |  |  |

| $\mathbf{A}$ | Mor        | e Experimental Result                                   | 88 |  |  |  |

|              | A.1        | IV Measurement of Other Chip                            | 88 |  |  |  |

|              | A.2        | Consumed Power of XRPIX2b                               | 88 |  |  |  |

|              | A.3        | Sense-node Capacitance                                  | 91 |  |  |  |

# List of Figures

| 1.1          | The normalized plot of the background counting rate by various satellite missions. | 2             |

|--------------|------------------------------------------------------------------------------------|---------------|

| 1.2          | Cross sectional view of the SOI pixel detector.                                    | $\frac{2}{3}$ |

| 2.1          | Probability of photon absorption for 300 $\mu m$ silicon as function of the photon | 10            |

| 2.2          | energy                                                                             | 10<br>12      |

| 2.3          | Principle model of CCD.                                                            | 14            |

| 2.4          | Schematic view of Medipix.                                                         | 15            |

| 2.5          | Cross sectional view of DEPFET.                                                    | 15            |

| 2.6          | Principle of single-photon counting detectors vs. integrating detectors            | 16            |

| 3.1          | The difference in a transistor model of bulk and SOI.                              | 21            |

| 3.2          | Radiation tolerance of single event effect (SEE)                                   | 21            |

| 3.3          | Schematic view of (a) Czochralski method and (b) Floating Zone method              | 22            |

| 3.4          | The process of Smart $Cut^{TM}$ technology by SOITEC                               | 23            |

| 3.5          | X-ray inspections of FZ-SOI wafers and slips.                                      | 24            |

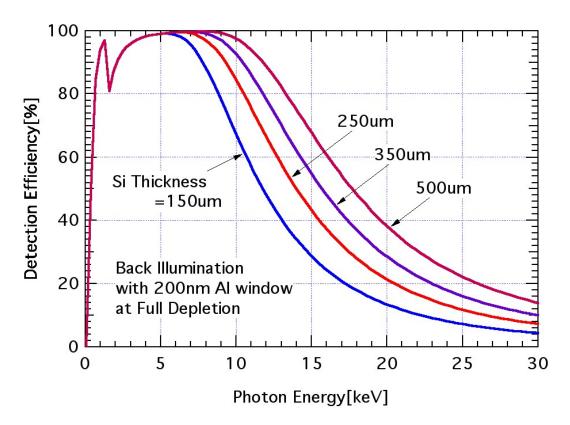

| 3.6          | Detection efficiency of X-ray energy by sensor thickness                           | 25            |

| 3.7          | SOIPIX issues.                                                                     | 26            |

| 3.8          | (a) Normal implantation method to create p-n junction in the substrate and         |               |

|              | (b) buried p-well implantation method                                              | 27            |

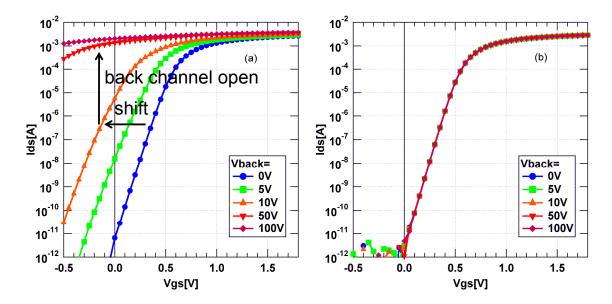

| 3.9          | NMOS transistor Ids-Vgs curve and back side voltage.                               | 28            |

| 3.10         | Cross sectional view of the SOI pixel process model                                | 29            |

| 3.11         | v i                                                                                | 29            |

|              | Stitching exposure.                                                                | 31            |

| 3.13         | Schematic view of Double SOI wafer                                                 | 31            |

| 4.1          | Concept of an active shield system with XRPIX                                      | 35            |

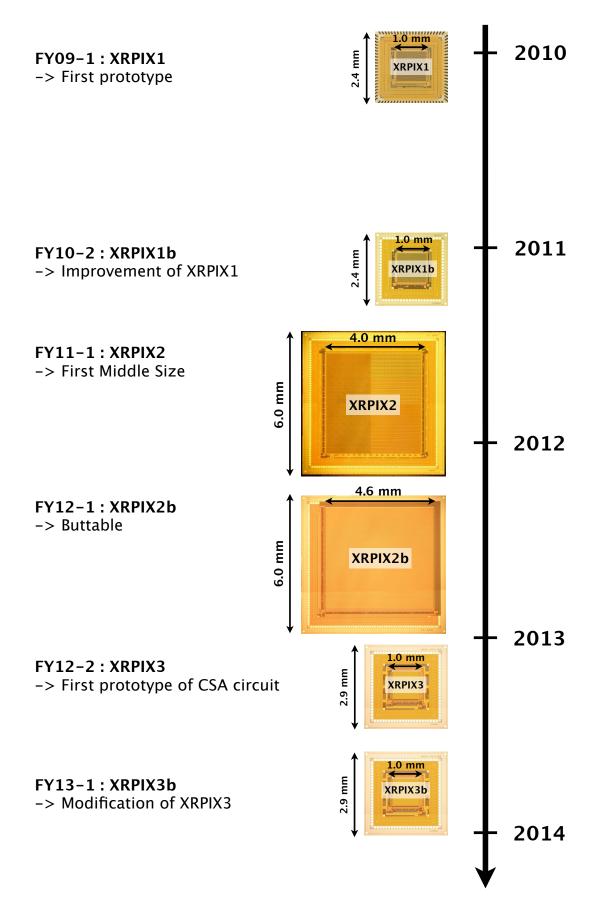

| 4.2          | XRPIX series history.                                                              | 37            |

| 4.3          | XRPIX2b chip photograph and block diagram.                                         | 39            |

| 4.4          | XRPIX3 chip photograph and block diagram.                                          | 40            |

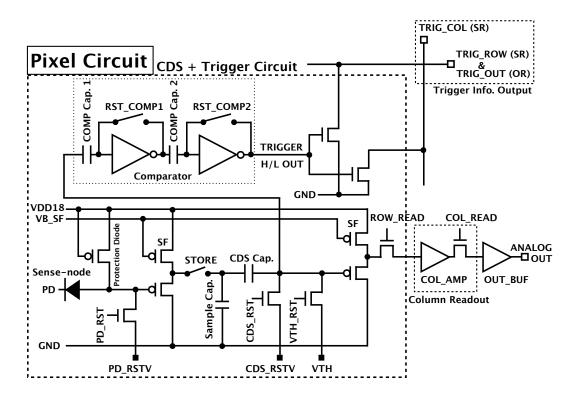

| 4.5          | Pixel circuit of the XRPIX2b.                                                      | 43            |

| 4.6          | Pixel circuit of the XRPIX3/3b                                                     | 44            |

| 4.7          | Pixel layout of the XRPIX2b.                                                       | 45            |

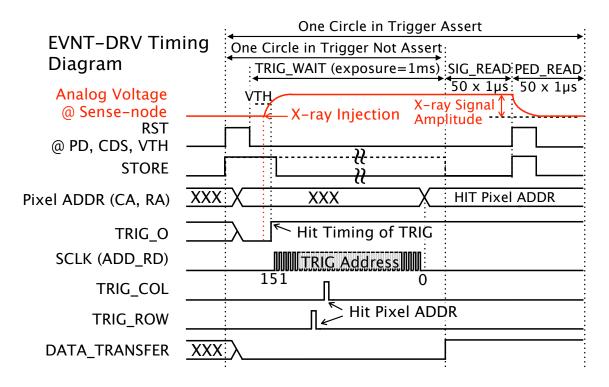

| 4.8          | Pixel operation timing diagram.                                                    | 46            |

| 4.9          | Flow of the event-driven readout mode.                                             | 47<br>47      |

| 4.10<br>4.11 | Timing diagram of XRPIX2b in event-driven readout mode                             | 47<br>48      |

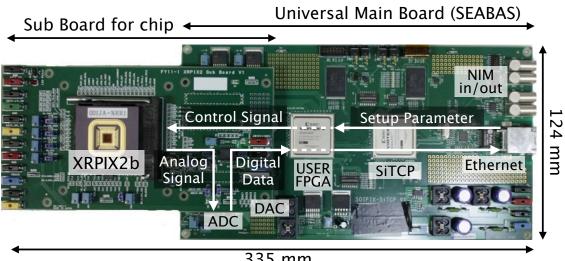

|              | General data acquisition system for SOI detectors, "SEABAS"                        | 48<br>49      |

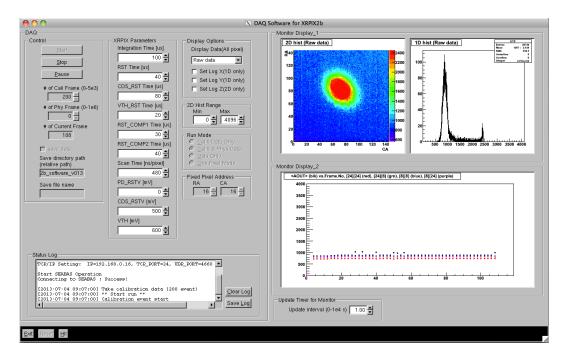

| 4.14         | Data acquisition solumate for $X_{11}$ $X_{20}$                                    | 49            |

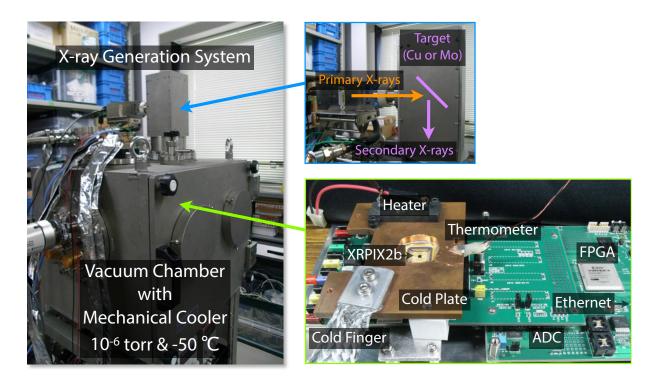

| 5.1        | Experimental setup of KEK                                                                 | 53 |

|------------|-------------------------------------------------------------------------------------------|----|

| 5.2        | Experimental setup of Kyoto University.                                                   | 53 |

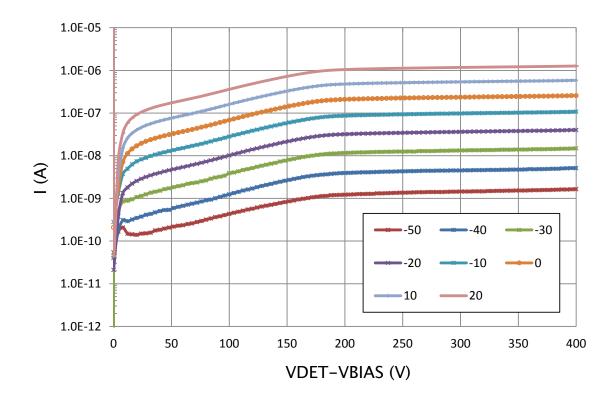

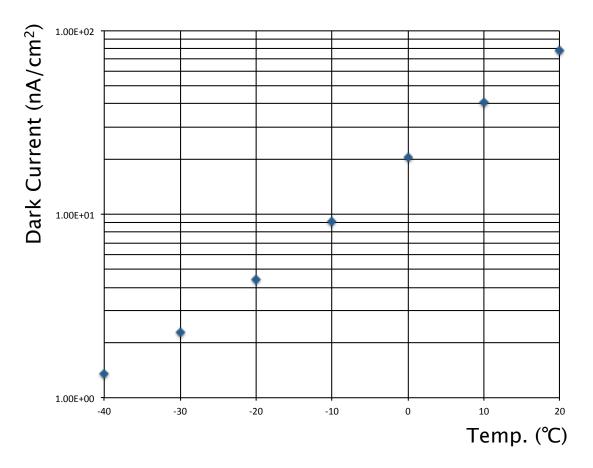

| 5.3        | I-V measurement of XRPIX2b                                                                | 54 |

| 5.4        | Temperature dependency of the dark current of the pixel part by XRPIX1b.                  | 55 |

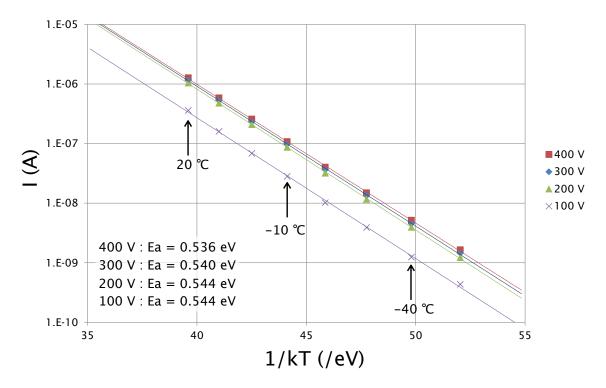

| 5.5        | Arrhenius plot of XRPIX2b                                                                 | 56 |

| 5.6        | The CV measurement of XRPIX2b                                                             | 57 |

| 5.7        | Consumed power measurement of XRPIX2                                                      | 57 |

| 5.8        | The measurement course of circuit gain.                                                   | 59 |

| 5.9        | Example of circuit gain measurement at 20 °C                                              | 59 |

| 5.10       | Results of XRPIX2b circuit gain measurements                                              | 60 |

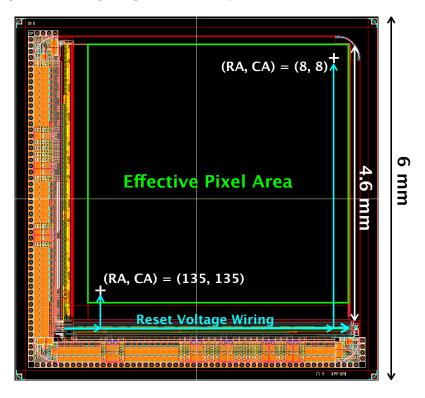

| 5.11       | The position on the observed chip of two points                                           | 60 |

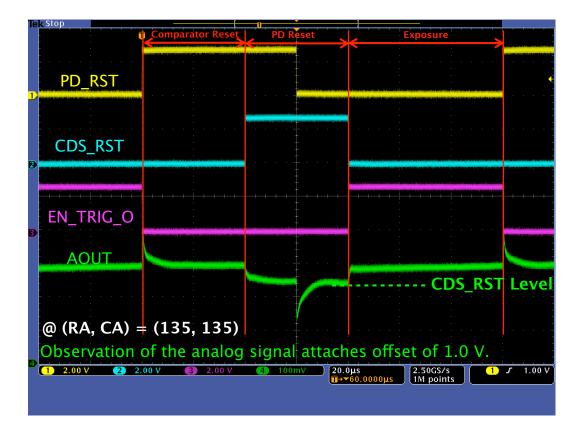

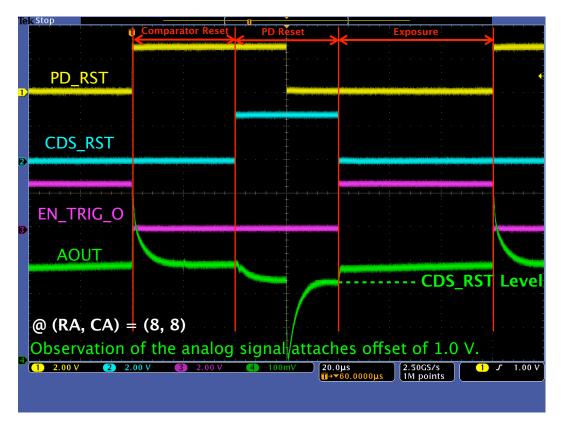

| 5.12       | Obtain waveform of pixel operation with the oscilloscope                                  | 61 |

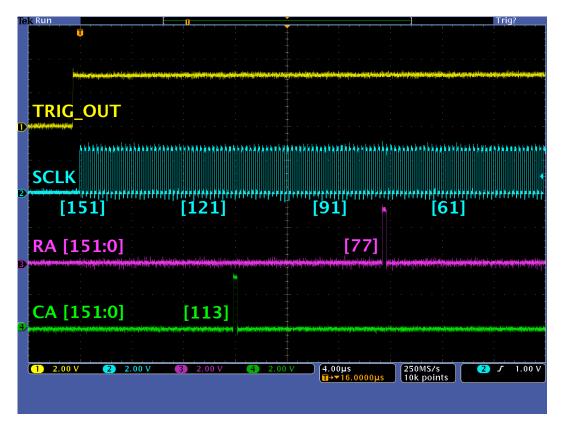

| 5.13       | Hit pattern information output by oscilloscope.                                           | 63 |

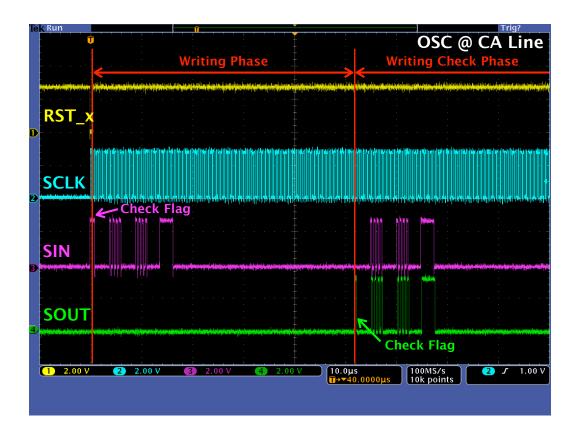

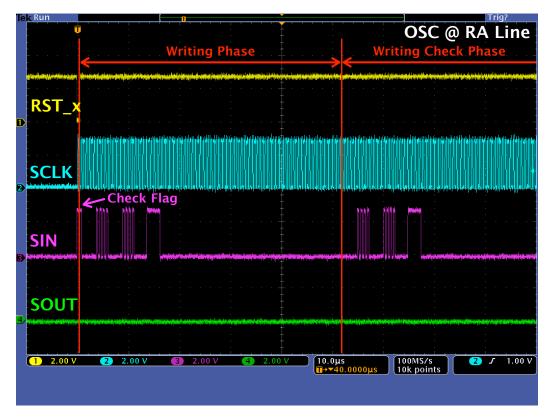

| 5.14       | Bad pixel mask and a control signal writing                                               | 64 |

| 5.15       | Schematic view of analysis method                                                         | 65 |

| 5.16       | X-ray spectra obtained in all pixel mode                                                  | 68 |

| 5.17       | X-ray energy calibration plot.                                                            | 69 |

| 5.18       | Calibration plot of Normal and CSA between X-ray energy and signal pulse                  |    |

|            | height                                                                                    | 69 |

| 5.19       | Comparison spectra of Normal and CSA pixel circuit by ${}^{55}$ Fe with all pixel         |    |

|            | mode                                                                                      | 70 |

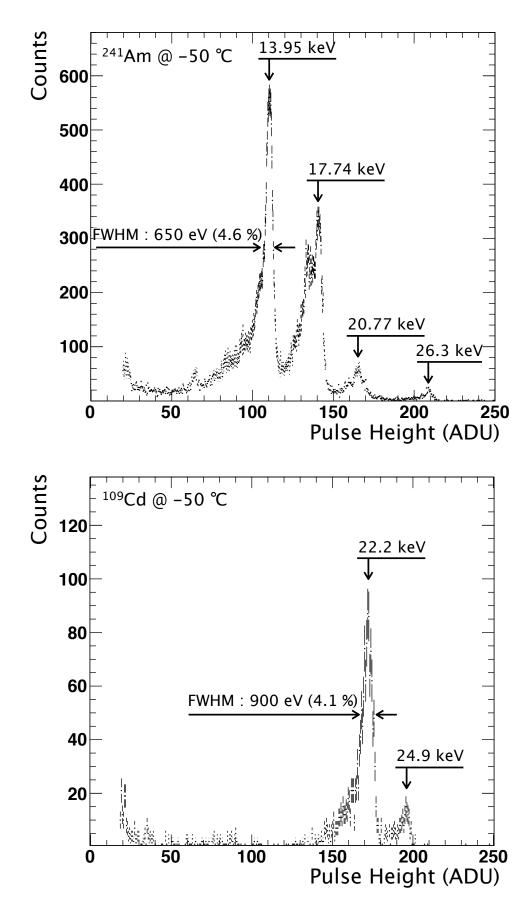

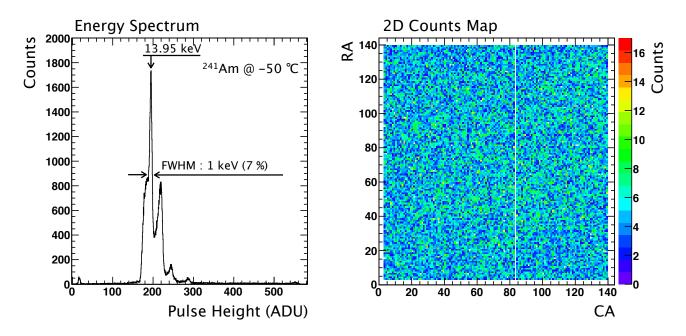

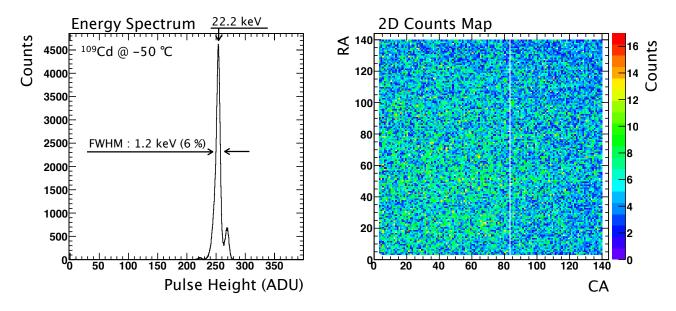

| 5.20       | X-ray energy spectrum of <sup>241</sup> Am by Event-Driven Mode                           | 72 |

| 5.21       | X-ray energy spectrum of <sup>109</sup> Cd by Event-Driven Mode                           | 72 |

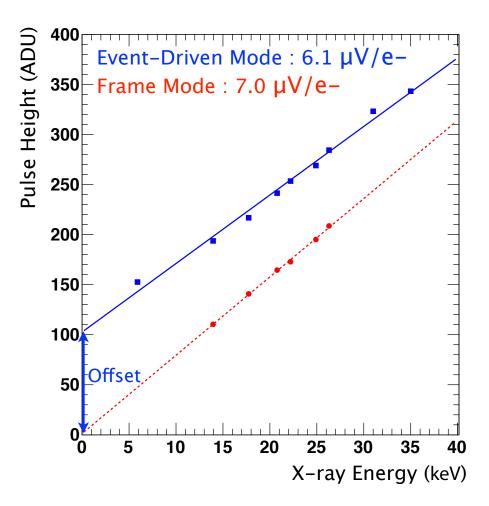

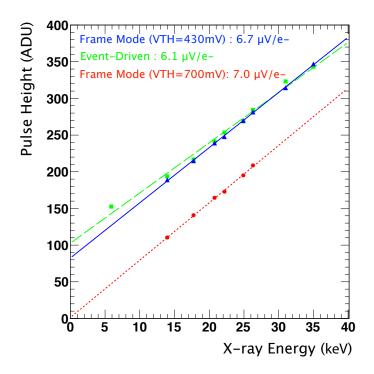

| 5.22       | Calibration between X-ray energy and signal pulse height (ADU)                            | 73 |

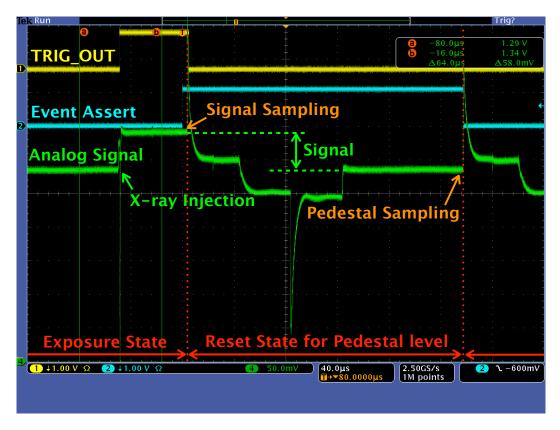

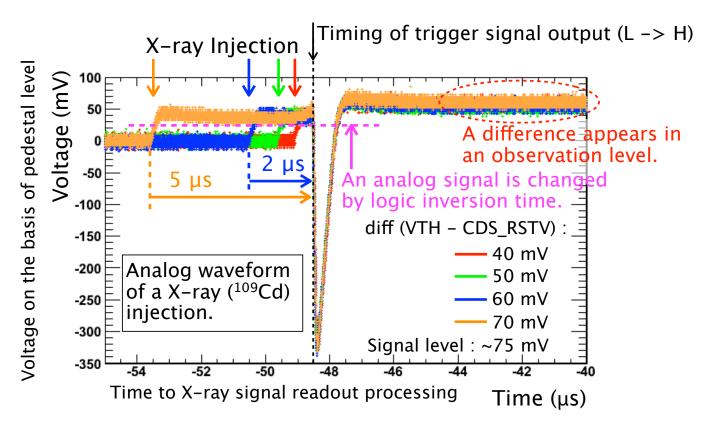

| 5.23       | The Event-Driven waveform when the X-rays injection from <sup>109</sup> Cd radio isotope. | 74 |

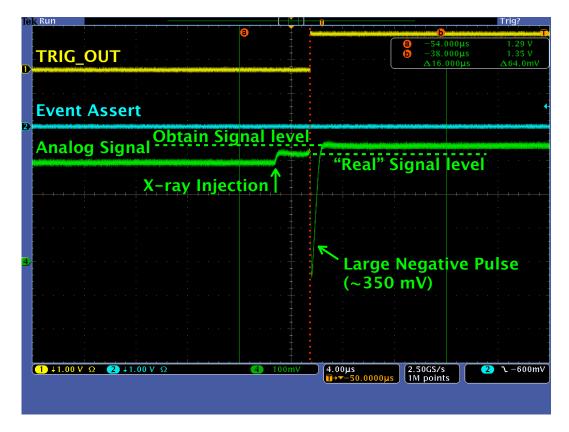

| 5.24       | The waveform which expanded the time of X-ray injection of Figure 5.23                    | 74 |

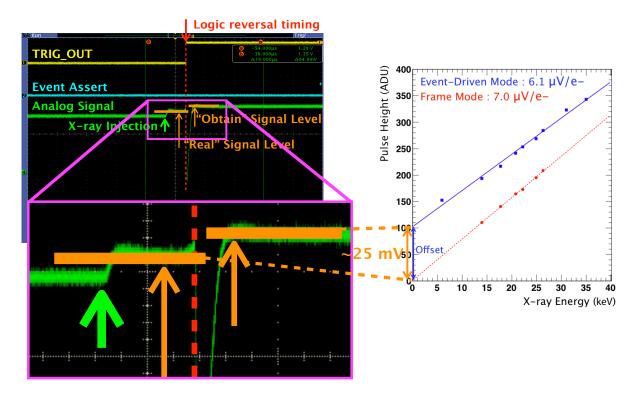

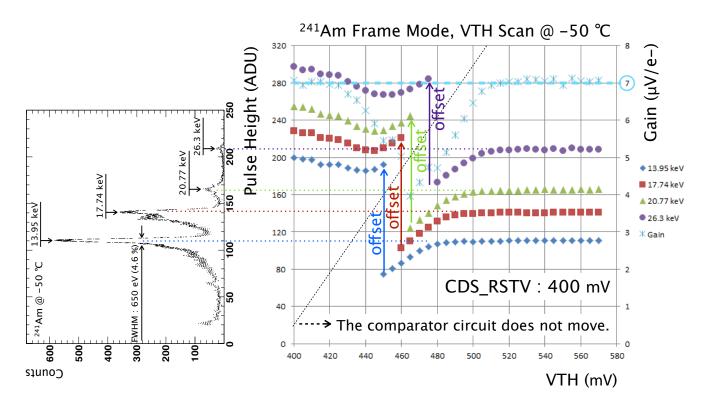

| 5.25       | About the difference of an observation signal level                                       | 76 |

| 5.26       | The waveform of X-ray injection of $^{109}$ Cd by changing a threshold voltage.           | 76 |

| 5.27       | Energy peak shift of <sup>241</sup> Am by changing a threshold voltage                    | 78 |

| 5.28       | Calibration between X-ray energy and signal pulse height (ADU)                            | 78 |

| 6.1        | The relation in the pixel layout of analog line, PD_RST signal, EN_TRIG_O                 |    |

| 0.1        | signal and sense-node (BPW).                                                              | 81 |

| 6.2        | The relation in the pixel and chip layout of COL_TRIG_OUT signal and                      | 01 |

| 0.2        | COL_OUT signal                                                                            | 82 |

| 6.3        | The block diagram of RA line registers.                                                   | 83 |

| 0.3<br>6.4 | History of readout noise with XRPIX series. And future expectation.                       | 85 |

| 0.4        | instory of readout hoise with Arti IX series. And future expectation                      | 00 |

| A.1        | I-V measurement of XRPIX2b in other case                                                  | 89 |

| A.2        | Arrhenius plot from Figure A.1                                                            | 89 |

| A.3        | Comsumed power measurement by comparison with XRPIX2                                      | 90 |

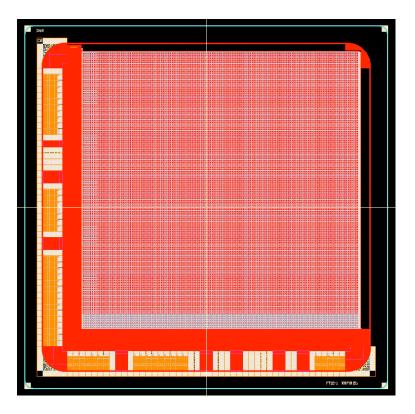

| A.4        | Layout design of XRPIX2b which applied BPW layer red.                                     | 90 |

# Acknowledgments

In advancing this study and my life, I have been indebted to many people. Although I would like to thank to all the people in this space, all those feelings cannot be written. Then, especially I describe below focusing on the person who was indebted by this study. I would like to express the deepest appreciation to my supervisor Prof. Yasuo Arai (KEK/IPNS) which is a project leader of SOIPIX group. He has given me many comments and helps. Furthermore, he has taught also about how to advance study. I would like to also appreciate Assistant Prof. Toshinobu Miyoshi, Ms. Yukiko Ikemoto of engineer, Mr. Kazuya Tauchi of engineer, Mr. Yowichi Fujita of engineer, Mr. Tetsuya Takahashi of technician (KEK/IPNS), and Mr. Daisuke Nio (KEK/SOKENDAI). Supports and comments of them were important in order to advance this study. I am deeply grateful to Prof. Takeshi Go Tsuru (Kyoto Univ.) which is a leader of XRPIX series. I would like to offer my special thanks to Assistant Prof. Takaaki Tanaka, Mr. Shinya Nakashima, Mr. Hideaki Matsumura (Kyoto Univ.), and Dr. Syukyo Gando Ryu (TOSHIBA Corp.). Support of Prof. Junji Haba which is a project leader of KEK Detector Technology Project (DTP) was invaluable to development of SOIPIX. Probably, it was not able to study without his encouragement.

I would like to acknowledge the valuable advice and great work by the personnel of LAPIS Semiconductor Co., Ltd. This work is supported by JSPS KAKENHI (21244040 and 23340047). This work is also supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys, Inc., Cadence Design Systems, Inc., and Mentor Graphics, Inc.

Thus, this study has been carried out by many support. Finally, I would like to express my gratitude to my family who supported until now.

> Ayaki Takeda February 2014

# Chapter 1

# Introduction

A celestial object exists in the universe countlessly and it is emitting various electromagnetic waves. However, some electromagnetic waves do not reach surface of the earth because they are scatted out or absorbed by the thick atmosphere. Therefore, it is necessary to launch observatories in orbit in order to observe photon (X-rays and  $\gamma$ -rays).

X-ray astronomy is the one of the important research fields to understand the universe. The first X-ray detection in the universes other than the Sun was observed with the rocket by B.Rossi and R.Giacconi in 1962. X-ray astronomy has grown quickly since then.

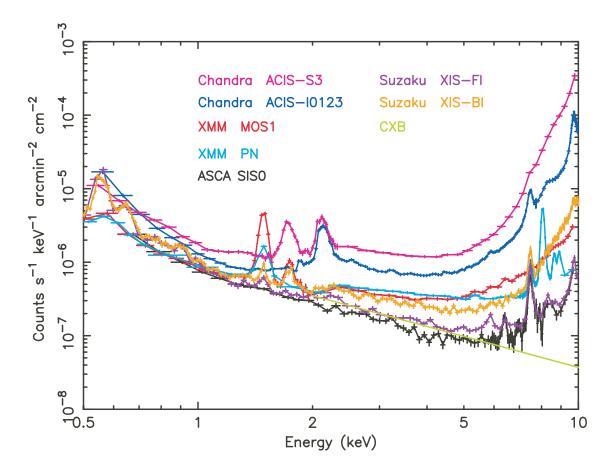

As of 2013, three X-ray astronomical satellites, Suzaku<sup>1</sup>, X-ray Multi-Mirror Mission  $(XMM-Newton)^2$ , and Chandra<sup>3</sup>, are operated in the space. The standard imaging spectrometers of these modern X-ray astronomical satellites are X-ray Charge Coupled Device's (CCD) [1]- [3]. The X-ray CCD offers Fano limited X-ray spectroscopic performance with the readout noise of about 3 electrons. It allows us to do wide and fine imaging with the sensor size of 20 - 30 mm square and a pixel size of ~ 30  $\mu$ m. However, it has some weakness. The most serious issue is a non-X-ray background (NXB) generated by high energy particles on orbit. Figure 1.1 is the background level of various satellite missions normalized by the effective area and unit solid angle. This shows that the background is dominated by the cosmic X-ray background (CXB) level below 6 keV. On the other hand, NXB become dominating component of the background above 6 keV. Especially it has serious influence above 10 keV. The rate of the NXB is too high to study faint sources. Therefore, a low background detector is desired in the next generation. Moreover, time resolution is too poor to make fast timing study of time variable sources (e.g., millisecond pulsar).

<sup>&</sup>lt;sup>1</sup>http://www.astro.isas.jaxa.jp/suzaku/index.html.en

<sup>&</sup>lt;sup>2</sup>http://xmm.esac.esa.int/

<sup>&</sup>lt;sup>3</sup>http://chandra.harvard.edu/

Figure 1.1: The normalized plot of the background counting rate by various satellite missions [4]. The background rate of *Suzaku*, *ASCA*, *XMM-Newton*, and *Chandra* adopted from Katayama et al. (2004) [5] are shown for comparisons.

Future X-ray astronomical satellite missions will require a new type of detectors that can distinguish X-rays and charged particle tracks, so as to reduce the background level. The new detector must have good coincidence time resolution (~ 1  $\mu$ s), superior hit-position readout time (~ 10  $\mu$ s) in order to reduce the NXB by cosmic rays. By introducing an anticoincidence method between the hit signal and the external active shield detector [6] [7], the background produced by the cosmic ray tracks [8] can be greatly reduced. This is particularly important for the observation of hard X-rays with energies above 10 keV. In addition, it must have wide bandpass (from soft to hard X-rays, 0.3 – 40 keV), and comparable performance in terms of imaging spectroscopy [9] [10].

Active pixel sensors (APSs) have attracted considerable attention recently for their improved performance, which is close to that of CCDs in terms of small pixel size and low readout noise [11]- [13]. The advantage of the APS is the ability to directly access the selected pixels, which results in a faster readout. Furthermore, the APS can generate a hit timing signal instantaneously; therefore, it can achieve much better timing resolution than

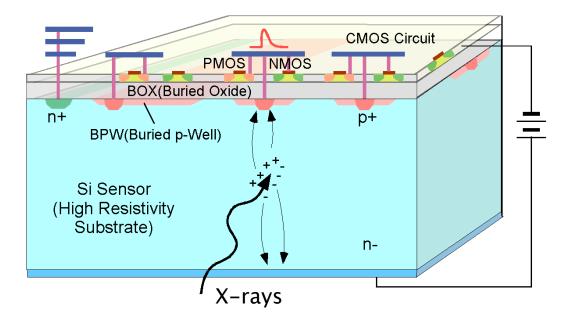

Figure 1.2: Cross sectional view of the SOI pixel detector.

CCDs. Hybrid pixel sensor like Medpix [14] is one of the candidates to realize above requirements. However, the spectroscopic performance of the sensor is limited by its counting type structure, and the yield is not so good due to the large number of bump bondings.

In order to realize the detector described above, we have been developing a new type of APS called XRPIX based on the semiconductor pixel detector with the silicon-on-insulator (SOI) complementary metal-oxide semiconductor (CMOS) technology. This new technology, i.e., SOI pixel detector (SOIPIX), has been developed by High Energy Accelerator Research Organization (KEK) in recent years. The SOI wafer is a bonding of two silicon wafers and a thin oxide film in between. The pixel detector consists of low resistivity silicon of a circuit and high resistivity silicon of a sensor. The SOIPIX utilize a thick handle wafer of SOI structure as a radiation sensor to detect charged particles and X-rays (Figure 1.2). Therefore, it is realized the ideal monolithic active pixel sensors. Thereby, we designed "Event-Driven SOIPIX" with a trigger information output function as "XRPIX series". And we realize the spectroscopy system which reduce background rate of the NXB by two orders of magnitude compared with the CCD. Finally, we aim to employ the XRPIX in the next generation X-ray astronomical satellite.

This thesis describe about basic development of the new detector for future X-ray astronomy. Furthermore, development of SOIPIX which is the new detector technology is also included. We designed this detector and show performance by evaluation of the prototype. The remaining part of the thesis proceeds as followings. In Chapter 2, we review the technology related to SOIPIX. Then, we describe our new semiconductor pixel detector with SOI technology, "SOIPIX" in Chapter 3. Moreover, we introduce my design, "XRPIX" which is event-driven type SOIPIX for future X-ray astronomical satellite mission in Chapter 4. In Chapter 5, we show the evaluation results of XRPIX. Finally, the discussion and the conclusion of this thesis are given in Chapter 6 and Chapter 7, respectively.

# References

- G. P. Garmire, M. W. Bautz, P. G. Ford, J. A. Nousek, and G. R. Jr. Ricker, "Advanced CCD imaging spectrometer (ACIS) instrument on the Chandra X-ray Observatory", in *Proc. SPIE*, Vol. 4851, pp. 28-44, 2003.

- [2] L. Strüder et al., "The European Photon Imaging Camera on XMM-Newton: The pn-CCD camera", Astronomy & Astrophysics, 365, L18, 2001.

- [3] K. Koyama et al., "X-Ray Imaging Spectrometer (XIS) on Board Suzaku", Publications of the Astronomical Society of Japan, 59, S23-33, 2007.

- [4] K. Mitsuda et al., "The X-Ray Observatory Suzaku", Publications of the Astronomical Society of Japan, 59, S1-7, 2007.

- [5] H.Katayama, "Properties of the background of EPIC-pn onboard XMM-Newton", Astronomy & Astrophysics, 414, S767-776, 2004.

- [6] T.Takahashi et al., "Hard X-Ray Detector (HXD) on Board Suzaku", Publications of the Astronomical Society of Japan, 59, S35-51, 2007.

- [7] M. Kokubun et al., "In-Orbit Performance of the Hard X-Ray Detector on Board Suzaku", Publications of the Astronomical Society of Japan, 59, S53-71, 2007.

- [8] T. Anada, T. Dotania, M. Ozaki, H. Murakami, "Instrumental background of the X-ray CCD camera in space: its dependence on the configuration parameters of CCD", in *Proc. SPIE*, 7011, 70113X (2008); doi:10.1117/12.788138.

- [9] S.G. Ryu et al., "First Performance Evaluation of an X-Ray SOI Pixel Sensor for Imaging Spectroscopy and Intra-Pixel Trigger", *IEEE Trans. Nucl. Sci.*, Vol.58, Issue:5, pp.2528-2536, 2011.

- [10] S. Nakashima, et al., "Progress in Development of Monolithic Active Pixel Detector for X-ray Astronomy with SOI CMOS Technology", *Physics Procedia*, vol. 37C, pp. 1392-1399, DOI: 10.1016/j.phpro.2012.04.100.

- [11] G. Prigozhin et al., "Characterization of Three- Dimensional-Integrated Active Pixel Sensor for X-Ray Detection", *IEEE Trans. Nucl. Sci.*, vol.56, no.11, pp.2602-2611, 2009.

- [12] N. Wermes et al., "New Results on DEPFET Pixel Detectors for Radiation Imaging and High Energy Particle Detection", *IEEE Trans. Nucl. Sci.*, vol.51, no.3, pp.1121-1128, 2004.

- [13] R. Ballabriga, M. Campbell, E. H. M. Heijne, X. Llopart, and L. Tlustos, "The Medipix3 Prototype, a Pixel Readout Chip Working in Single Photon Counting Mode With Improved Spectrometric Performance", *IEEE Trans. Nucl. Sci.*, vol.54, no.5, pp.1824-1829, 2007.

- [14] R. Plackett et al., "Current status of the Medipix2, Timepix, Medipix3 and Timepix2 pixel readout chips", PoS, VERTEX2010, 030, 2010.

- [15] M. Kokubun et al., "Hard X-ray Imager (HXI) for the ASTRO-H mission", in Proc. SPIE, 7732, 773215 (2010); doi:10.1117/12.857933.

# Chapter 2

# **Review of Pixel Detector Technology**

In order to understand a radiation semiconductor detector, it is necessary to get to know about a semiconductor and interaction with a radiation. Obviously, it corresponds also to the SOIPIX detectors. This chapter describes these contents briefly. Moreover, existing pixel detectors other than the SOIPIX detectors are also introduced.

### 2.1 Semiconductor Physics

#### 2.1.1 p-n Junction

The reversely biased p-n junction is the basic building block of silicon sensors. It builds up an electric field that collects the signal charge and suppresses the leakage current, an important noise source. A pixel sensor is a reversely biased p-n diode with a highly segmented cathode or anode.

#### 2.1.2 Depletion Region

A depletion region is made by p-n junction. In this region, the electric field which goes to p-type from n-type has occurred. The electron-hole pairs generated in this region moves by an electric field. And the electron-hole pairs generated outside this region disappears by re-combination. Therefore, this region is important in order to detect charged particles and photons. The depletion region spreads by applying the reverse bias voltage of p-n junction.

#### **Depletion Depth**

The depth of a depletion region is calculable. The depth  $x_p$  and  $x_n$  of depletion region in a p-type and n-type semiconductor, respectively,

$$x_p = \sqrt{\frac{2\epsilon(V+V_{bi})}{qN_A(1+N_A/N_D)}}, \ x_n = \sqrt{\frac{2\epsilon(V+V_{bi})}{qN_D(1+N_D/N_A)}}$$

(2.1)

$\epsilon$  is a permittivity of semiconductor. In case of silicon,  $\epsilon$  is  $1.0 \times 10^{-12}$ . V is a reverse bias voltage.  $V_{bi}$  is a built-in potential of p-n junction. q is a elementary charge (=  $1.602 \times 10^{-19}$ ).  $N_D$  is a donor concentration and  $N_A$  is an acceptor concentration. Then, the depletion depth,  $W_{dep}$  is shown by

$$W_{dep} = x_p + x_n = \sqrt{\frac{2\epsilon(V + V_{bi})}{q} \left(\frac{1}{N_D} + \frac{1}{N_A}\right)}$$

(2.2)

The case of the p-n junction of a general semiconductor detector is considered. That is, a large difference is to donor concentration and acceptor concentration  $(N_D \ll N_A)$ . Thus,  $W_{dep}$  is

$$x_p = \sqrt{\frac{2\epsilon(V+V_{bi})}{qN_A^2}} \ll x_n = \sqrt{\frac{2\epsilon(V+V_{bi})}{qN_D^2}} \simeq W_{dep}$$

(2.3)

In this case, the depletion region spreads in n-type semiconductor. Furthermore, by using Formular (2.3) and resistivity of n-type semiconductor,  $\rho = 1/q\mu N_D$ ,  $W_{dep}$  is

$$W_{dep} = \sqrt{2\epsilon\mu\rho(V+V_{bi})} \tag{2.4}$$

$W_{dep}$  is proportional to the square root of resistivity of silicon wafer and reverse bias voltage from this formula.

#### **Depletion Capacitance**

A depletion region is served as a capacitor. The capacitance of this region,  $C_{dep}$  is calculable. The junction depletion region capacitance per unit area is defined as

$$C_{dep} = \frac{dQ}{dV} = \frac{dQ}{\frac{dQ}{\epsilon}W_{dep}} = \frac{\epsilon}{W_{dep}}$$

(2.5)

, where dQ is the incremental change in depletion region charge per unit are for an incremental change in the applied voltage dV. By using Formula (2.4), Formula (2.5) is

$$C_{dep} = \sqrt{\frac{\epsilon}{2\mu\rho(V+V_{bi})}}$$

(2.6)

Furthermore, when it changes about V,

$$V = \frac{\epsilon}{2\mu\rho} \cdot \frac{1}{C_{dep}^2} - V_{bi} \tag{2.7}$$

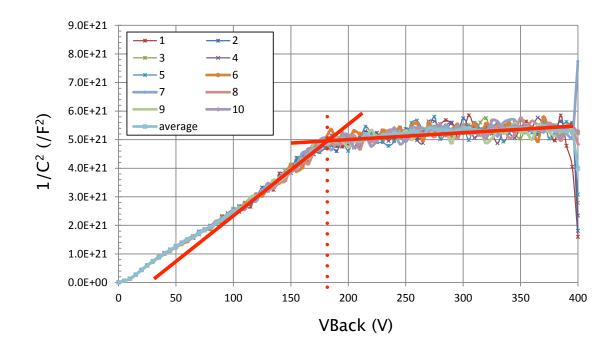

From this, V is proportional to  $1/C_{dep}^2$ . This relation is used by CV measurements (Section 5.3).

### 2.2 Radiation

#### 2.2.1 Photon Interactions

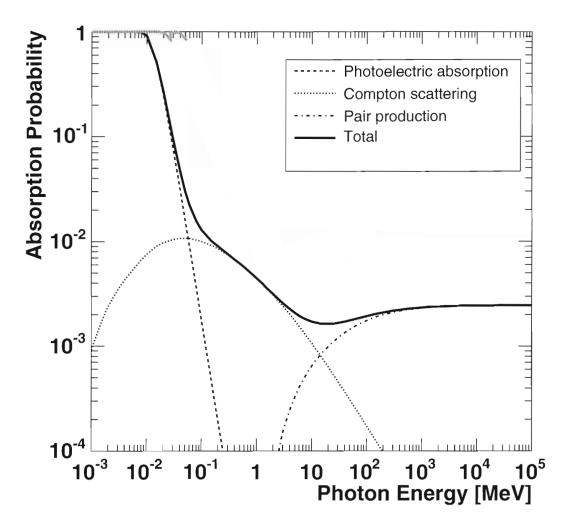

#### Photoelectric Absorption

The photo electric effect is the absorption of a photon by an atomic electron which is hence moved into the conduction band. It is the dominant process at low photon energies, in silicon below about 100 keV as shown in Figure. Its cross section is very strongly dependent on the nuclear charge Z of the absorbing material: with n varying between 4 and 5 depending on the photon energy. For this reason high-Z materials like cadmium telluride are preferred for X-ray detection. Silicon is used for photon detection up to energies of about 100 keV [1].

#### **Compton Scattering**

At higher energies the photoelectric cross section drops down several orders of magnitude and scattering processes become more important. The cross section of Compton scattering is only linearly dependent on Z.

#### **Pair Production**

At energies exceeding twice the electron mass pair production also contributes to the cross section and becomes the only important process at energies exceeding 10 MeV.

Figure 2.1: Probability of photon absorption for 300  $\mu$ m silicon as function of the photon energy. Contributions from different process are indicated [1].

#### 2.2.2 Charged Particle Interactions

#### **Ionization Loss**

Charged particles deposit a part of their energy through many scattering processes with electrons of the absorbing material along the particle track. This process is dominant for particles heavier than electrons and described by the *Bethe-Bloch formula* :

$$-\left\langle \frac{dE}{dx}\right\rangle = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left(\frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 + \cdots\right),\tag{2.8}$$

$\frac{dE}{dx}$  is energy loss of the particle usually given in  $\frac{eV}{g/cm^2}$ . K is  $4\pi N_{Ave}r_e^2m_ec^2$  (= 0.307 MeV cm<sup>2</sup>). z is charge of the traversing particle in units of the electron charge. Z is atomic number of absorption medium (14 for silicon). A is atomic mass of absorption medium (28 for silicon).  $m_ec^2$  is rest energy of the electron (0.511 MeV).  $\beta$  is velocity of the traversing particle in units of the speed of light.  $\gamma$  is Lorentz factor  $1/\sqrt{1-\beta^2}$ . I is mean excitation energy (137 eV for silicon) [1].

#### 2.2.3 Fano Factor

The average number of electron-hole pairs, N, generated for a constant amount of absorbed energy, e.g., caused by a radio isotope of X-rays, can be calculated by dividing the absorbed energy E by the average energy necessary to produce one electron-hole pair, w:

$$N = \frac{E}{w} \tag{2.9}$$

The energy w required to create an electron-hole pair is about 3.65 eV in silicon. This value, which is more than three times larger than the band gap of 1.12 eV, is a material property and does hardly depend on the type and energy of the radiation if the latter is much larger than the band gap. The difference generates phonons, which in the end will dissipate as thermal energy.

The fraction of deposited energy that is used for electron-hole separation and phonon generation is subject to fluctuations which N to vary by

$$\left\langle \Delta N^2 \right\rangle = FN = F\frac{E}{w} \tag{2.10}$$

with F begin the *Fano factor*. If the fraction of the absorbed energy used for the electronhole pair generation would be fixed, their number N would also be fixed and the value of F would be zero. The Fano factor F, however, is, according to theoretical works, in the order of ~0.1 for most semiconductors and determines the best possible energy resolution of semiconductor sensors in spectroscopic applications.

The energy resolution of a detector is decided by the statistical fluctuation of an electron obtained and equivalent noise charge (ENC) of readout circuit.  $\Delta E_{FWHM}$  is shown by

$$\Delta E_{FWHM} = 2.35w \sqrt{E_{\gamma}(F+f)/w + \sigma^2}$$

(2.11)

$E_{\gamma}$  is a photon energy. F is a *Fano factor*. f is a statistics factor showing the amplification effect. Since amplification is not performed in the case of silicon, f is 0.  $\sigma$  is an ENC of readout circuit. A value in case  $\sigma$  of Formula (2.11) is zero is a spectroscopic performance limit, i.e., Fano limit of a detector [1].

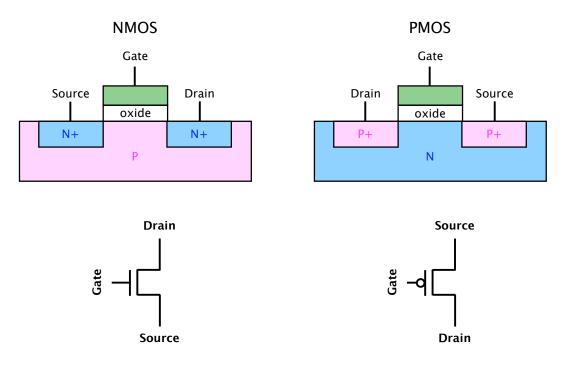

Figure 2.2: Cross sectional view and symbol of NMOS and PMOS (e.g., CMOS).

### 2.3 Analog CMOS Circuit

#### 2.3.1 CMOS

The circuit by CMOS is used for a large-scale integration (LSI) circuit. It consists of NMOS and PMOS which are the contrastive pairs of metal oxide semiconductor field effect transistors (MOSFETs). Figure 2.2 shows the cross sectional view and symbol of NMOS and PMOS transistors. "N" and "P" shows n-type and p-type semiconductors respectively. The analog and the digital circuit consist of combination for these. The symbol of Figure 2.2 is used with the circuit schematic of this thesis.

#### 2.3.2 Clock Feedthrough

In analog CMOS circuit, a MOS switch couples the clock transitions to the sampling capacitor through its gate-drain or gate-source overlap capacitance. The effect introduces an error in the sampled output voltage. Assuming the overlap capacitance is constant, we express the error as

$$\Delta V = V_{CK} \frac{WC_{ov}}{WC_{ov} + C_{H}}$$

(2.12)

where C is the overlap capacitance per unit width. The error V is independent of the input level, manifesting itself as a constant offset in the input / output characteristic. As with charge injection, clock feedthrough leads to a trade-off between speed and precision as well.

### 2.3.3 kT/C Noise

The kT/C noise is a reset noise. A similar effect occurs in sampling circuits. The onresistance of the switch introduces thermal noise at the output and, when the switch turns off, this noise is stored on the capacitor along with the instantaneous value of the input voltage. It can be proved that the rms voltage of the sampled noise in this case is still approximately equal to kT/C.

### 2.4 Other Pixel Detector Technology

The technology of some pixel detectors has been developed until now. Some typical silicon semiconductor detectors are introduced in this section. It is common that these collect the electric charges (electron-hole pairs) generated by the interaction with silicon. These differences are the methods of processing as a subsequent signal. In the following sections, they are also described.

#### 2.4.1 CCD

One of the pixel detectors used for a long time has the charge coupled device (CCD). This is detectable in a wide-band from visible light to X-rays. As the Chapter 1 described, it is a standard detector also in X-ray astronomy. It was invented in 1969 at Bell Labs by Willard Boyle and George E. Smith. The principle of operation is transmitting an electric charge, and reads it as a signal. Figure 2.3 shows this principle model. The pixel size is several  $\mu$ m to about tens of  $\mu$ m. It has high spectroscopic performance. However, manufacture is difficult because of a complicated structure. Moreover, it is very expensive. Therefore, it is being transposed to a CMOS image sensor in recent years.

#### 2.4.2 Medipix

The VLSI front-end prototype chip (Medipix) has been developed at the European Organization for Nuclear Research (CERN) [3]. Development of this detector was started from the

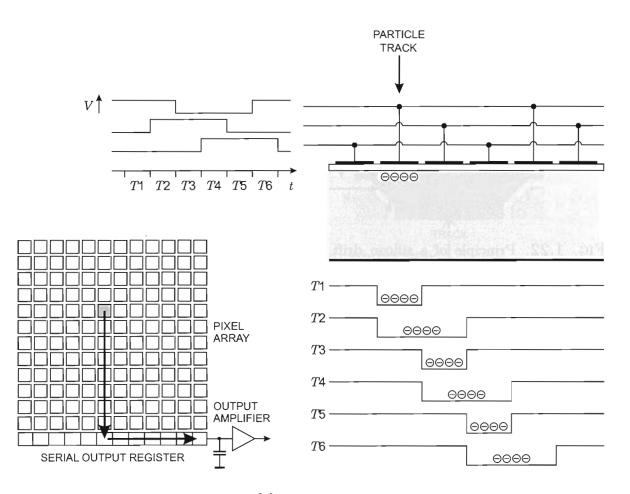

Figure 2.3: Principle model of CCD [2]. Upper right: schematic cross-sectional view of a CCD. Voltages are applied to the electrodes according to the timing diagram at the upper left. The potential sequence shifts the charge from the track to the right Three electrodes comprise one pixel, but all charge from the track subtended by the pixel is drawn to the pixel's left-most electrode. Six clock periods shift the charge to the neighboring pixel. The pixels are read out sequentially (bottom left). Charge is transferred down the transferred to the readout line by the output amplifier.

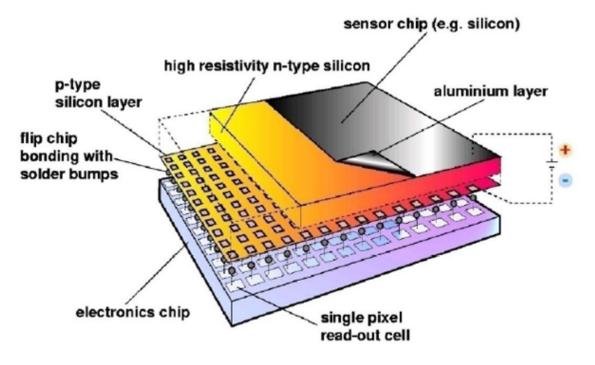

latter half of the '90s. It is used as a radiation pixel detector of a high energy experiment and X-ray imaging. Figure 2.4 is a schematic view of Medipix. It is the structure of making a sensor and readout circuit independently and connecting them by a metal bump (i.e., Hybrid type detector). The pixel size is 55  $\mu$ m square [5]. Operation of a detector is a counting type. The module by a USB interface also exists in this detector.

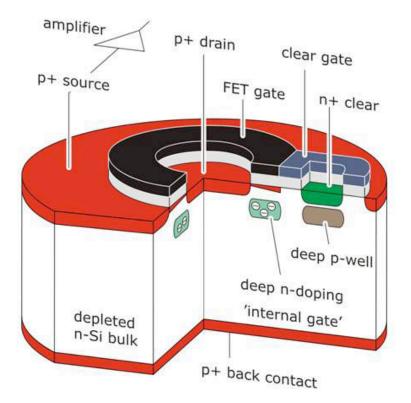

#### **2.4.3** DEPFET

The DEPleted-Field Effect Transistor (DEPFET) principle has been proposed in 1985 at Max-Planck-Institut (MPI), Germany by Kemmer and Lutz [6]. It is used as a radiation pixel detector of a high energy experiment (e.g., Belle II and ILC experiment [7]) and a future X-ray astronomical satellite mission (e.g., *Athena*+ [8]). It is a monolithic active

Figure 2.4: Schematic view of Medipix [4].

Figure 2.5: Cross sectional view of DEPFET [8].

Figure 2.6: Principle of single-photon counting detectors vs. integrating detectors.

pixel detectors. Figure 2.5 shows the structure of DEPFET. The pixel size is about 25  $\mu$ m. The characteristics of this detector is operation by "internal gate" and "clear gate". This detector collects the generated electric charges to a internal gate, and reads the signal according to the number of electric charges. The electric charge held at the internal gate is drawn out from a clear gate.

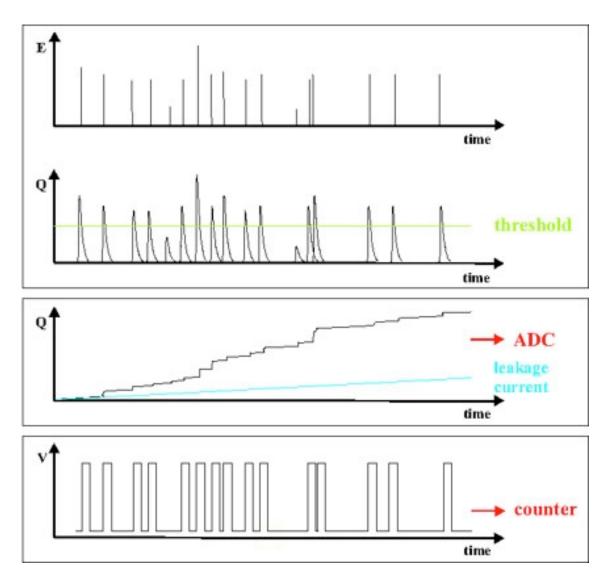

#### 2.4.4 PILATUS

At the Swiss Light Source (SLS)<sup>1</sup> at the Paul Scherrer Institut (PSI) in Switzerland, a single photon counting pixel detector called PIxeL ApparaTUs for the SLS (PILATUS) has been developed for X-ray applications since 1997 [9]- [11]. Figure 2.6 shows the principle of single

<sup>&</sup>lt;sup>1</sup>http://www.psi.ch/sls/

photon counting. This is also the detector proved about the usefulness of photon counting in X-ray imaging. The PILATUS is established as a product and is sold from DECTRIS Ltd.<sup>2</sup> which is founded by 2006. This has wide-spread in the market as application of X-ray imaging.

### 2.4.5 MIMOSA

In the early 1990s a monolithic active pixel sensors (MAPS) was proposed. This detector, called Minimum Ionising particle MOS Active pixel (MIMOSA) [12], is developed as virtex detector of a high energy experiment (e.g., ILC experiment). It is used of the epitaxial layer of standard CMOS processes as detecting sensitive volume.

$<sup>^{2} \</sup>rm https://www.dectris.com/$

# References

- [1] L. Rossi, et al., "Pixel Detectors", 2005.

- [2] H. Spieler, "Semiconductor Detector Systems", 2005.

- [3] S.R. Amendolia, E. Bertolucci, M.G. Bisogni, U. Bottigli, A. Ceccopieri, M.A. Ciocci, M. Conti, P. Delogu, M.E. Fantacci, P. Maestro, V. Marzulli, E. Pernigotti, N. Romeo, V. Rosso, P. Rosso, A. Stefanini, S. Stumbo :MEDIPIX: a VLSI chip for a GaAs pixel detector for digital radiology, Nucl. Instr. and Meth. A422 (1999) 201-205.

- [4] Medipix2 Home Page. https://medipix.web.cern.ch/medipix/pages/medipix2.php

- [5] R. Ballabriga, M. Campbell, E. Heijne, X. Llopart, L. Tlustos, W. Wong :Medipix3: A 64 k pixel detector readout chip working in single photon counting mode with improved spectrometric performance, Nucl. Instr. and Meth. A633 (2011) S15-S18.

- [6] J. Kemmer and G. Lutz :NEW DETECTOR CONCEPTS, Nucl. Instr. and Meth. A253 (1987) 365.

- [7] DEPFET Collaboration. http://www.hll.mpg.de/twiki/bin/view/DEPFET/WebHome.

- [8] Athena+ Collaboration. : The Wide Field Imager (WFI) for Athena+.

- [9] B. Henrich, A. Bergamaschi, C. Broennimann, R. Dinapoli, E. F. Eikenberry, I. Johnson, M. Kobas, P. Kraft, A. Mozzanica and B. Schmitt :PILATUS : A single photon counting pixel detector for X-ray applications, Nucl. Instr. and Meth. A607 (2009) 247-249.

- [10] P. Kraft, A. Bergamaschi, Ch. Broennimann, R. Dinapoli, E. F. Eikenberry, B. Henrich, I. Johnson, A. Mozzanica, C. M. Schlepuz, P. R. Willmott and B. Schmitt : Performance of single-photon-counting PILATUS detector modules, J. Synchrotron Rad. 16 (2009) 368-375.

- [11] Takeyoshi Taguchi, Christian Bronnimann, and Eric F. Eikenberry, NEXT GENERA-TION X-RAY DETECTORS FOR IN-HOUSE XRD

- [12] R. Turchetta, et al., :A monolithic active pixel sensor for charged particle tracking and imaging using standard VLSI CMOS technology, Nucl. Instr. and Meth. in Phys. Res. A 458 (2001) 677.

# Chapter 3

# **SOI** Pixel Detector

The SOI pixel detector (SOIPIX) is the key technology of this thesis. This development was started originally for the particle tracker in the high-energy physics experiments. However, it is soon revealed that the detector also has great potential as X-ray detectors. In this chapter, we describe this new detector development and technology.

### 3.1 Development of SOI Pixel Detector

In the high-energy physics experiment, semiconductor pixel detectors are widely used and located near the interaction point of colliding beams in order to know the track of particles with high accuracy. At present, the pixel detectors used in the experiment are consist of the sensor and circuit substrates, and those are connected by metal bumps (i.e., Hybrid type detector). This is that it is difficult to build both radiation sensor and circuit in a single substrate. Radiation sensors need thick depletion region, so high-voltage and highresistive wafer are required. On the other hand, CMOS LSI circuits work only in low-voltage environment and low-resistive wafer is used to avoid latch-up effect etc.

However, the hybrid structure has many drawbacks. For example, it has limitation of spatial resolution by the size of the bump bondings, high multiple scattering probability due to its excessive material, and low signal speed by large parasitic capacitance. In addition, the cost of the bump technology is high due to its low yield. On the other hand, the monolithic type detector solves those disadvantages of the hybrid type. It is a detector with the structure which a sensor and readout circuit unified. However, since high resistivity silicon cannot be used for a circuit, it is difficult to obtain a thick depletion layer. In order to conquer all of these problems, a new detector is desired for future experiments.

In Detector Technology Project (DTP) of KEK a new project to develop a semiconductor pixel detector using the SOI technology was started. It is called SOIPIX, and has been developing from 2005 [1]. The SOIPIX utilize a thick handle wafer of SOI structure as a radiation sensor to detect charged particles and X-rays. The SOI wafer is a bonding of two silicon wafers and a thin oxide film in between. Thus optimum resistivity can be selected for sensing part and circuit part respectively. By making contacts between top and bottom silicon through an oxide film, it becomes the detector which unify a sensor and readout circuitry. This is the reason that the SOIPIX is called "ideal" monolithic pixel sensor.

The SOIPIX has many advantages. For example, the mechanical bump bonding does not exist. Therefore, this is high density, low parasitic capacitance, and high sensitivity. Moreover, sensor thickness can be adjusted with polish of a sensor wafer from the thin depletion layer of a high energy experiment ( $\sim 50 \ \mu$ m) to the thick depletion layer of Xray application ( $\sim 500 \ \mu$ m). This can have a complex circuit in each pixel because this is composed of standard CMOS circuit. Additionally, the price cutting can be expected because of based on industrial standard technology. Thus, SOIPIX can be applied to the high energy experiments, astrophysics, medical imaging and so on [2].

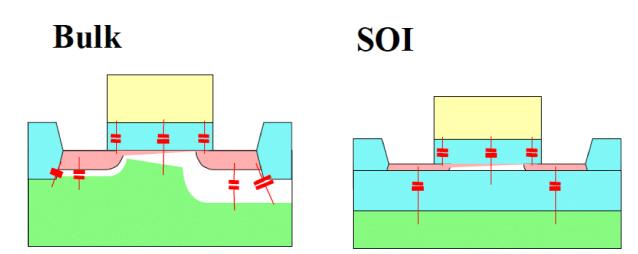

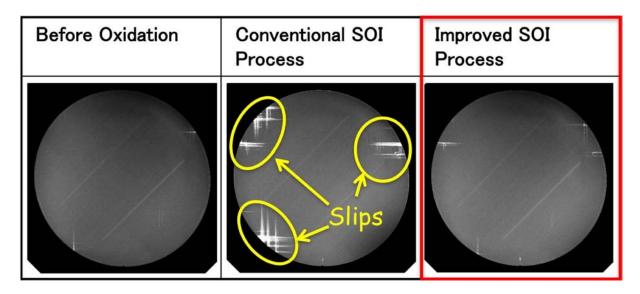

### 3.2 SOI Technology

SOI technology is growing greatly as a CMOS LSI process of the industry in recent years. This is because it has many advantages as compared with the bulk CMOS usually used. For example, high speed operation (i), low consumed power (ii), high integration (iii), latch-up immunity (iv), operate in wide temperature (4 - 570 K) range (v), single event effect (SEE) tolerance (vi), and so on. Figure 3.1 is the difference in a transistor model of bulk and SOI. The big feature of SOI structure is that each transistor is separated by the insulating layer of SiO<sub>2</sub>, i.e., buried oxide (BOX). Thereby, the parasitic capacitance between elements decreases greatly ((i), (ii), (iii)) and SOI is suitable also for an integrated circuit like CPU which needs high-speed operation. Furthermore, the leakage current between elements and through a substrate is lost ((ii), (iii)). Moreover, the temperature dependency of SOI of the threshold voltage of a transistor is low (v). The ionization damage by radiation affects operation of a transistor. Since bulk layer of SOI CMOS is small as compared with bulk CMOS, there is little generation of the electric charge which causes SEE (Figure 3.2, (vi)).

Figure 3.1: The difference in a transistor model of bulk and SOI. The left side is a bulk (normal) process. The right side is a SOI process. The SOI transistor of parasitic capacitance is smaller than bulk.

Figure 3.2: Radiation tolerance of single event effect (SEE).

Thus, existence of BOX layer gives the big benefit for a transistor.

### 3.3 Process of SOI Wafer

In this section, we introduce the Czochralski and Floating Zone method which is a typical generation method of a silicon single crystal, the Smart Cut<sup>TM</sup> process which is a typical generation method of a SOI wafer, and the high resistivity SOI wafer which becomes important with SOIPIX.

#### 3.3.1 Czochralski Method

The method of introducing first is Czochralski (Cz). Single crystalline substrates are typically differentiated by the process by which they are made. The Cz wafers are the most

Figure 3.3: Schematic view of (a) Czochralski method and (b) Floating Zone method [3].

commonly used type of silicon wafer, and are used by both the solar and integrated circuit industry. Of course, we also use well. The process of making a large single crystalline silicon ingot by the Czochralski process is shown below. The use of quartz crucibles in the manufacture of Cz substrates causes the incorporation of ppm  $(10^{18} \text{ cm}^{-3})$  oxygen into the silicon ingot. The oxygen itself is relatively benign but creates complexes with boron doping that degrades the carrier lifetime. N-type ingots fabricated with phosphorous dopants have similar oxygen concentrations but do not show the degradation effect nor do wafers with lower resistivity or gallium dopants.

#### 3.3.2 Floating Zone Method

The method of obtaining a crystal with high purity, i.e., high resistivity is the Floating Zone (FZ) method rather than obtained by the usual Cz method. By high-frequency heating, a new single crystal is grown up by melting few cm of width. Cz wafers contain a large amount of oxygen in the silicon wafer. On the other hand, in order not to use crucibles, this process method tends to maintain purity. Therefore, we need the wafer by FZ method, in order to obtain a thick depletion layer.

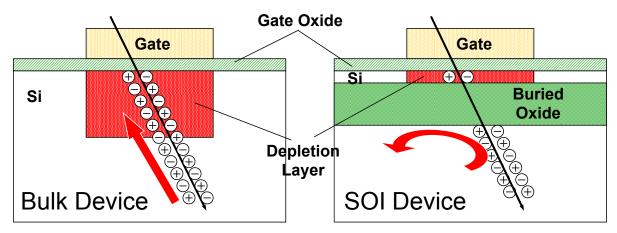

Figure 3.4: The process of Smart Cut<sup>TM</sup> technology by SOITEC [6]. SOIPIX uses the special SOI wafer which has the process of the handle wafer with the high resistivity silicon wafer.

### 3.3.3 Smart Cut<sup>TM</sup> Process

Although there are some methods of creating a SOI wafer, Smart Cut<sup>TM</sup> by SOITEC is mainly used now. This process was developed by M.Bruel of CEA-LETI in 1991. Figure 3.4 shows this process technology. First, two initial silicon wafers (A and B) are prepared for Smart Cut<sup>TM</sup> process. In the case of SOIPIX, they are different resistivity wafer in which the circuit (wafer A) is low and the sensor (wafer B) is high (1). Next, the wafer A is oxidized to create insulating layer (2). Then, a hydrogen ion is implanted into the wafer A to induce formation of an in-depth weakened layer. By adjusting the implant energy of ion, the thickness of a SOI layer can be changed (3). After implantation, both wafers A and B are cleaned to eliminate any particle and surface contaminants and to make both surfaces hydrophilic. Thereby, they are united as one silicon wafer (4). This wafer splits in the place which poured in hydrogen ions by heating to 400 – 600 °C (5). By annealing and chemical mechanical polishing (CMP), SOI wafer is completed (6). Furthermore, seed wafer becomes new wafer A (7). The process of the SOI wafer for SOPIX is specially made from utilizing the handle wafer in which resistivity differs.

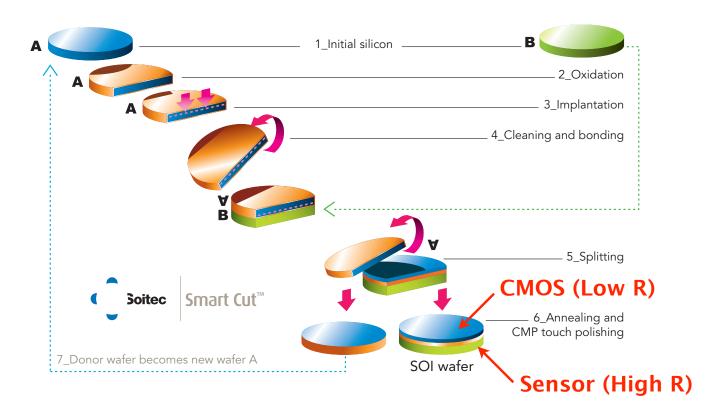

Figure 3.5: X-ray inspections of FZ-SOI wafers and slips.

### 3.3.4 High Resistivity SOI Wafer for SOIPIX

In order to realize a pixel detector with SOI wafer, it is necessary to make a handle wafer with high resistivity. Thereby, a depletion layer can be grown up on more low back bias voltage of sensor. From the early stages of development, the high resistivity wafer offered by the standard process of SOITEC is mainly used. This handle wafer is made in Cz method, which is n-type and has about 700  $\Omega \cdot$  cm resistivity. However, it is desirable to obtain much higher resistivity to create thicker depletion region with lower voltage. Then, we requested SOITEC and had the special SOI wafer by bonding with FZ wafer. As a result of the challenge, it was not easy to make FZ-SOI wafer of 8 inch.

Figure 3.5 shows X-ray inspections of FZ-SOI wafers. In the original process, the FZ-SOI wafer has some lattice defect (i.e., slips) which CMOS high temperature process causes into a wafer (Figure 3.5 center). After careful tuning of the high temperature process, the FZ-SOI wafer without the major slips was realized (Figure 3.5 right). The resistivity of handle wafer has about 7 k $\Omega \cdot$  cm. Furthermore, n-type and p-type have completed FZ-SOI wafer. The resistivity of handle wafer has about 40 k $\Omega \cdot$  cm. Therefore, three kinds of wafers (Cz n-type, FZ n-type, and FZ p-type) are available for SOIPIX. The results of this thesis mainly treats SOIPIX by Cz-SOI wafer (Cz-SOIPIX). Incidentally, handle wafers other than silicon (e.g., cadmium telluride (CdTe) or germanium (Ge)) do not exist for the reason of a process line.

Figure 3.6: Detection efficiency of X-ray energy by sensor thickness.

### 3.4 SOI Pixel Process

The SOIPIX is realized based on the existing SOI technology currently used in industry. Therefore, the new process to make a pixel detector needed to be developed. This process called "SOI pixel process", and joint development with LAPIS Semiconductor Co., Ltd.<sup>1</sup> which is a leading company about SOI process in Japan. The company name of LAPIS Semiconductor Co., Ltd. changed from OKI Semiconductor Co., Ltd. in September, 2011. Our SOI pixel process is developed based on their 0.2  $\mu$ m CMOS fully-depleted (FD-) SOI process. Thanks to the process line of a company, the quality of the process which realizes SOIPIX has been achieved. In this section, we introduce SOI pixel process currently used by SOIPIX.

#### 3.4.1 Structure of SOIPIX

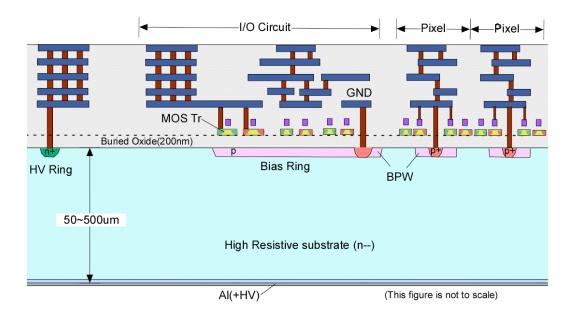

The component of SOIPIX is three layers, a circuit, BOX, and a sensor, and they are dependent on the structure of SOI wafer. The SOI wafer currently used for the process is a wafer of SOITEC and Shin-Etsu Chemical Co., Ltd.<sup>2</sup> The thickness of a circuit layer is

<sup>&</sup>lt;sup>1</sup>http://www.lapis-semi.com/en/

<sup>&</sup>lt;sup>2</sup>http://www.shinetsu.co.jp/en/

# Back Gate Hole Trapping Cross Talk

Figure 3.7: SOIPIX issues.

40 nm and BOX layer is 200 nm. The sensor layer is limited by the thickness of the handle wafer, and is 725  $\mu$ m at the maximum. Although thickness is controllable by mechanical grinding a handle wafer, it can be made thin to 50  $\mu$ m until now. Usually, the thickness of the sensor layer of Cz-SOIPIX is 260  $\mu$ m and FZ-SOIPIX is 500  $\mu$ m, respectively. On the back side of a sensor layer, chemical etching, impurities implant, laser annealing, and vapor-deposition of aluminum (200 nm) as an electrode are processed. The thickness of a sensor layer influences detection efficiency. It is important for especially X-ray application to have a thick depletion region. The detection efficiency of SOIPIX is calculable as normal silicon. Figure 3.6 shows detection efficiency of X-ray energy by sensor thickness. In order to detect the X-rays of higher energy, the sensor layer needs to obtain a thicker depletion region. This is realizable by two or more stacks of SOIPIX.

SOIPIX has some issues from the structure. They are three phenomena, back gate effect (BGE), hole trapping, and cross talk. The BGE is a difficult problem which must be solved to build SOIPIX. When high voltage is applied to the sensor, the threshold voltage of a transistor shifts under the influence of the electric field, and it become ON, i.e., stops working as a circuit. This is because the layer of a sensor and a circuit is in a very near place ( $\sim 200$  nm). In order to shield the electric field from sensor voltage to a transistor, a new structure of Buried Well (BW) and its process method were developed (see Section 3.4.2). This technology was the very big technical innovation for SOIPIX.

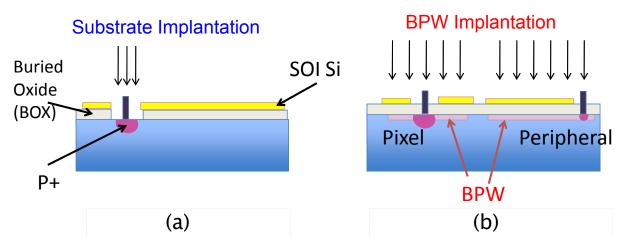

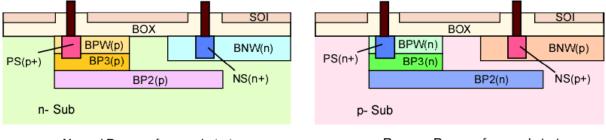

Figure 3.8: (a) Normal implantation method to create p-n junction in the substrate and (b) buried p-well implantation method. By fixing the BPW potential under peripheral circuit, the back gate effect is completely suppressed. In the pixel area, BPW may be used extend sensor area.

As the Section 3.2 described, the tolerance SEE is high, however, the problem to a hole trapping is not avoided. This phenomenon is a damage by accumulation of the radiation called Total Ionizing Dose (TID). A hole trap occurs by ionization in BOX. A circuit stops working normally by the shift of the threshold voltage of a transistor, and formation of a back channel in response to the influence of the electric charge. In the electrode of p-n junction and circuit, capacitive coupling is built by BOX. This affects a circuit, when the electric charges generated in the sensor layer are collected (i.e., cross talk). Although hole trapping and cross talk are not fatal, operation of a detector is affected not a little. These phenomena are improved by Double SOI (D-SOI) technology under present development (see Section 3.6.2).

#### 3.4.2 Buried P-Well

As the Section 3.4.1 described, it is important to suppress BGE in order to realize SOIPIX. This was a big problem in early stages of development. The structure devised in order to solve this problem is Buried P-Well (BPW). This is the structure which made thin p layer in the sensor layer under BOX layer. By fixing the potential of this p layer, the shield of the electric field from voltage applied to a sensor layer is built. Figure 3.8 shows process method of BPW implantation. First, a hole is created by etching of BOX layer and a normal implantation is introduced into the by accelerating the impurity ions to high-energy level in order to form p-n junction in the substrate (Figure 3.8 (a)). Next, the BOX layer is formed by introducing p layer without removing a top silicon layer (Figure 3.8 (b)). Usually,

Figure 3.9: NMOS transistor Ids-Vgs curve and back side voltage. (a) Without BPW layer, (b) with BPW layer connected to ground. By introducing the BPW layer, the back gate effect is fully suppressed.

peripheral circuitry is fixed BPW layer to a grand level. Thereby, the back gate effect is completely suppressed. In the pixel area, the potential of BPW is a reset voltage level of a sensor. Therefore, the potential is completely unfixable. However, although there is potential change at the time of charge collection, it works as a shield of an electric field. In the pixel area, BPW may be used extend sensor area.

Figure 3.9 shows the plot of NMOS transistor Ids-Vgs curve and back side voltage. When there is no BPW layer, the output of NMOS transistor changes with the influences of the voltage applied to the sensor (Figure 3.9 (a)). In case of fixing BOX layer to a grand level, the output does not change (Figure 3.9 (b)). This plot shows that BGE is completely suppressed by introduction of the BPW layer.

#### 3.4.3 Circuit Layer

The circuit layer of SOIPIX is fundamentally the same as the usual SOI process. A difference is existence of contact to the electrode of a sensor layer. Therefore, the layout of a detector can be designed like the usual SOI CMOS only by including this contact. Figure 3.10 shows the 0.2  $\mu$ m FD-SOI pixel process for SOIPIX. The Core and I/O valtage are 1.8 and 3.3 V, respectively. This process has 5 metal layers for trace and 1 active layer (CMOS transistor). Moreover, metal-insulator-metal (MIM) capacitance (1.5 fF/ $\mu$ m<sup>2</sup>) can consist of 3-4 metal layers. Furthermore, there is normal and low threshold transistors are available

Figure 3.10: Cross sectional view of the SOI pixel process model.

Normal Process for n- substrate

Reverse Process for p- substrate

Figure 3.11: Structure of the sensor layer for n-substrate and p-substrate. Capital letters are layer name and inside of brackets shows actual doping.

for both core and IO transistors. The transistor model of structure are available three type, Body-floating, Source-tie and Body-tie.

## 3.4.4 Sensor Layer

In the sensor layer, the electrode is formed by p-n junction at the BOX interface, and it is made to connect with a circuit layer through via. In the present process, this electrode is called PS and NS. After introduction of BPW/BNW layers (Section 3.4.2) successfully, several additional structures implanted into a deeper sensor layer were proposed and introduced. Figure 3.11 shows present possible layers under the BOX layer. BP3 is same mask layer used in the BPW, and is used when deeper implant is required. BP2 is deepest buried layer to create nested structure with the BNW.

# 3.5 Multi Project Wafer Run

The cost of semiconductor process is not cheap. Major part of the cost is mask set. To reduce development cost and have multiple chances for developments, we decided to operate this SOI pixel process as Multi Project Wafer (MPW) runs. In past a few years, we have been doing the MPW runs twice per year except year 2011 when large earthquake was occurred and Lapis semiconductor fab was damaged.

In addition to many Japanese institutes, we have been collaborating with US / Europe / Asian researchers through this MPW runs. In 2011, we changed the mask size from 20.6 mm  $\times$  20.6 mm to 24.6 mm  $\times$  30.8 mm, so that we can accept more designs and build larger detector.

# 3.6 Development of Advanced SOIPIX Technology

In order to realize a more high specification detector, we are developing the new technology of advanced SOIPIX. In this section, we describe some technology currently developed.

#### 3.6.1 Stitching

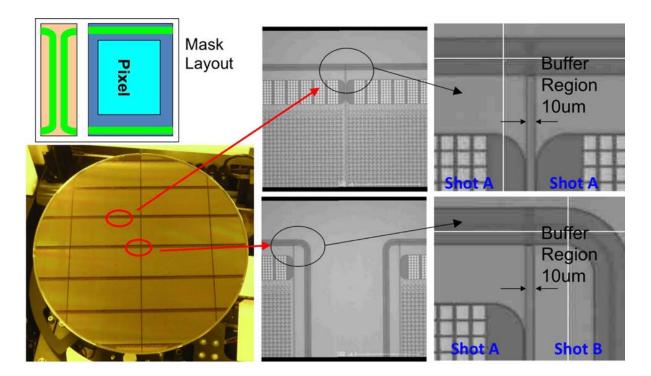

Large area detectors are often required in some experiments, but the mask size is limited to  $20.4 \text{ mm} \times 30.8 \text{ mm}$  in size now. Therefore, we have developed stitching technique to make large format detector by using only one mask set. Figure 3.12 shows the stitching method and photographs of the processed wafer.

The development is mainly driven by Riken group for the SOPHIAS detector. Since this was our first trial, we took buffer region size of 10  $\mu$ m and connect only minimum number of layers (PS, NS and metal 1). However, Lapis is confident to make buffer region shorter and connects all metals.

### 3.6.2 Double SOI Wafer

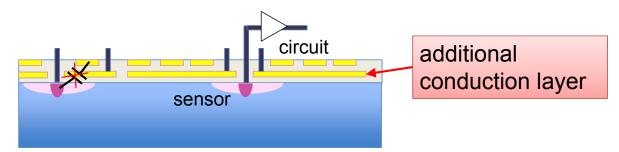

As the Section 3.4.1 described, two problems, radiation tolerance of the detector and crosstalk between sensor-node and SOI CMOS circuit, still remain in SOIPIX. The cross talk generates the unintended signal and the circuit causes unstable operation or mistaken operation. Although the influence of SEE is small, it has influence of TID for SOIPIX. Now,

Figure 3.12: Stitching exposure for the SOPHIAS detector. Both edge structure and pixel structure and pixel structure were drawn in a mask. Part of the mask is blocked during exposure. In this detector (SOPHIAS), pixel layout was repeated 3 times and edge structures are exposed at both ends.

Figure 3.13: Schematic view of Double SOI wafer.

radiation tolerance is about 2 kGy. However, many applications require more than 10 kGy (1 Mrad) tolerance. In space, radiation tolerance is unnecessary compared with the high energy physics experiment. Though, it is important to suppress the cross talk.

In order to solve these problems, introduction of the another conduction (middle silicon) layer between sensor and circuit was considered. Figure 3.13 shows schematic view of this concept. This new SOI wafer is called Double SOI (D-SOI) wafer. Thereby, a cross talk can be suppressed by fixing the potential of middle silicon. Furthermore, by applying the potential of minus to middle silicon, the shift of the threshold voltage by a hole trap can be setoff. Therefore, performance of SOIPIX as a detector improves greatly by introducing

middle silicon.

The first D-SOI wafers were produced by SOITEC with n-substrate. Moreover, second D-SOI wafers have been produced by Shin-Etsu Chemical Co., Ltd., Japan, with p-type substrate. The SOIPIX with D-SOI wafer is already realized and the device is under evaluation now. By introducing D-SOI wafer, BGE can be suppressed without using BPW layer. This becomes reduction of sensor capacitance, i.e., the improvement in a gain.

# References

- [1] SOIPIX Collaboration. http://rd.kek.jp/project/soi/.

- [2] Y. Arai, et al., "Development of SOI pixel process technology", Nucl. Instrum. Methods, Volume 636, Issue 1, Supplement 1, Pages S31-S36, 2011.

- [3] S.M.Sze, "SEMICONDUCTOR DEVICES Physics and Technology 2nd Edition"

- [4] G.K.Celler, Sorin Cristoloveanu, "Frontiers of silicon-on-insulator"

- [5] G.Celler, M.Wolf, "Smart Cut<sup>TM</sup> A guide to the technology, the process, the products-", SOITEC, 2003.

- [6] http://www.soitec.com/pdf/Soitec\_SmartCut\_EN.pdf

# Chapter 4

# **Design for X-ray Astronomy**

For future X-ray astronomical satellite mission, we have been developing a new detector based on SOIPIX technology. It realizes a new operation called Event-Driven readout mode by intra-pixel trigger signal. In this chapter, we introduce the design and specification of this detector.

# 4.1 Concept

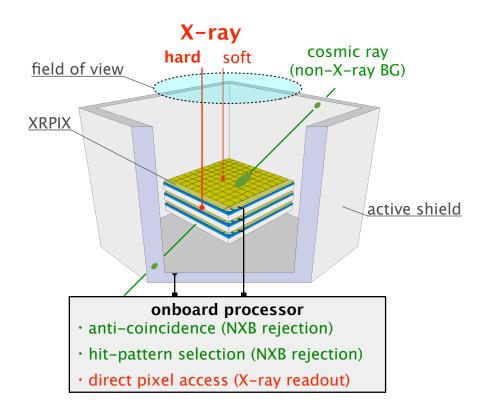

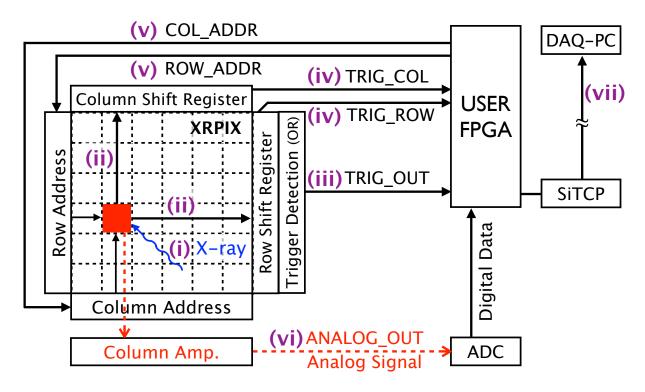

The new detector for X-ray astronomy must have high coincidence time resolution (~ 1  $\mu$ s), superior hit-position and signal readout time (~ 10  $\mu$ s) in order to reduce a NXB by cosmic rays, and wide bandpass (from soft to hard X-rays, 0.3 – 40 keV) in terms of imaging spectroscopy (Chapter 1). In order to realize this performance, we have been developing a new APS based on SOIPIX, called XRPIX. It has a comparator circuit in each pixel. Therefore, it can generate a trigger signal of timing and a hit-position when X-rays and charged particles signal crosses the threshold voltage of the pixel. This can realize new operation called "Event-Driven readout mode" which judges whether it is a "real X-ray signal" for every detection events.

Figure 4.1 shows the concept of the XRPIX imaging spectroscopy system with an active shield which consists of scintillation counters. Most importantly, the anti-coincidence system with an active shield (rejection with timing) and the X-ray hit-pattern selection (rejection of events spread over pixels caused by charged particles), both of which can be realized with the APS, is expected to reduce the space NXB in the hard X-ray band. Furthermore, highspeed readout is also realized because only the pixel which detected X-rays direct access

Figure 4.1: Concept of an active shield system with XRPIX to reduce the NXB by cosmic rays. The active shield can be a scintillation counter (e.g., a BGO) read out by avalanche photodiodes (APDs).

and reads a signal by the hit position information obtained from XRPIX.

The anti-coincidence system is important for reject NXB. The X-ray signals which are a candidate for observation condense by the mirror and come from the upper part of XRPIX. On the other hand, XRPIX have to remove NXB which comes from various directions. First, NXB from the upper part is discriminable with the trigger timing signal from several stack XRPIXs. The other NXB is discriminable with the trigger timing signal from an active shield and XRPIXs. There are two cases in this NXB with what is the charged particle itself, and is the X-ray of fake signals generated by the interaction of charged particle with the lens barrel. Thus, the NXB is identified by the coincidence of the trigger timing signal from XRPIXs and an active shield; i.e., X-ray signals are discriminable by anti-coincidence with NXB. Additionally, the detection efficiency over high energy X-rays also improves by two or more stacks of XRPIX.

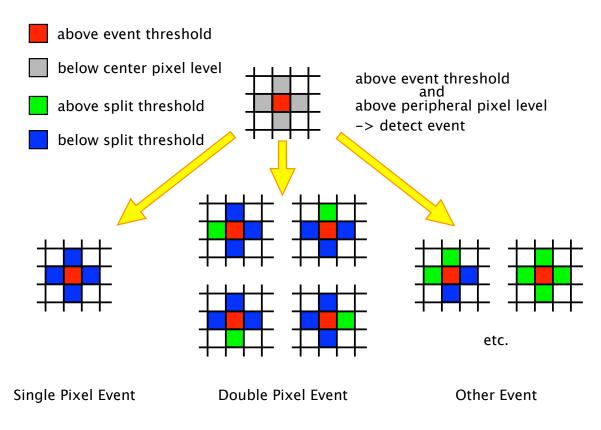

Furthermore, NXB is also excluded by a hit-pattern selection. X-rays generate electronhole pairs to a narrow region by an interaction. As a result, a hit pattern becomes only one or two pixels. On the other hand, charged particle events spread over in the wide area pixels. Therefore, it can be judged with a hit-pattern whether it is NXB. If the hit-pattern selection is simple, it can be processed in the digital circuit of XRPIX, and it can also perform advanced processing by reading to external FPGA. By XRPIX, the highly efficient detector which have high spectroscopic performance and fast signal readout is realized in the future.

# 4.2 XRPIX Series

As the Section 4.1 described, XRPIX is Event-Driven SOIPIX which can readout analog signal only from hit pixel. There are no other detectors which can perform such operation in the world. In this section, we describe the history of XRPIX series.

### 4.2.1 XRPIX Project

XRPIX project started in 2009 with the Kyoto University. The basic structure of XRPIX is the same as that of the integration-type SOIPIX. Furthermore, it has trigger generation function. XRPIX series has designed six devices of XRPIX1/1b/2/2b/3/3b until now (Figure 4.2). All the devices have been designed by changing a pixel circuit, structure, a chip size, and so on. XRPIX1 to XRPIX2b were designed as a prototype for realizing event-driven readout mode, and XRPIX3/3b was designed for improvement spectroscopic performance. They were fabricated using the 0.2  $\mu$ m FD-SOI CMOS pixel process by LAPIS Semiconductor Co., Ltd. We designed all the devices except XRPIX1. Moreover, we also developed FPGA for XRPIX control, and DAQ software. In the following sections, we describe the specification of each device.

### 4.2.2 XRPIX1