# Minimising Makespan of Discrete Controllers: A Qualitative Approach

by

Ezequiel Gustavo Castellano

#### Dissertation

submitted to the Department of Informatics in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

The Graduate University for Advanced Studies, SOKENDAI March 2020

## Acknowledgments

I would like to thank my advisor Prof. Nobukazu Yoshioka, as well as my subadvisors Prof. Shin Nakajima and Prof. Hiroyuki Kato of the Graduate University of Advanced Studies. I would also like to acknowledge the examiners Prof. Kenji Tei, Prof. Nicolás D'Ippolito and Prof. Fuyuki Ishikawa. I am gratefully indebted to them for their very valuable comments on this thesis.

I would also like to extend my deepest gratitude to Prof. Victor Braberman and Prof. Sebastián Uchitel of the University of Buenos Aires. Their ideas were the inspiration for my research direction. In particular, I would like to thank Victor for keep following my research closely and always giving me great advice.

I am also grateful to the National Institute of Informatics and the Japanese government for honoring me with a scholarship that made my studies possible. I would also like to extend this thanks to the University of Buenos Aires and the government of Argentina, who provided me with strong background to do my studies abroad through free education. Free education does not guarantee same opportunities for everyone, but it is one step forward to equality.

Huge thanks should also go to all my friends and people I met in the last years. Friends are always there to listen when you are having hard times, to celebrate victories, or to just be there. My most sincere thanks go to my friends from *El Pelle*, UBA courses, UBA futsal, LaFHIS, TIEC, NII and many other life friends. I would like to list each of them individually, but I do not want the acknowledgments to be longer than the rest of this thesis.

Special thanks to my family for providing me with unfailing support and continuous encouragement throughout my entire life. My deepest gratitude to *mi mamá* Silvia, *mi papá* Rafa, *mi hermana* Cyntia y *mi abuela* Dora. Through life, the environment changes yourself, but your familiy are the ones that give you the basis to move through that environment.

Last but not least, I would also like to thank Linguang, *el amor de mi vida*, for always being next to me supporting me at times of stress, but most importantly for joining me in this adventure called life. This thesis would not be possible without her support.

Ezequiel Castellano

P.S.: Thanks to you that you are reading me now. Shall I say sorry instead?

# Committee

| Advisor Dr.                  | YOSHIOKA Nobukazu                                              |  |

|------------------------------|----------------------------------------------------------------|--|

| Professor of                 | of National Institute of Informatics/SOKENDAI                  |  |

|                              | NAKAJIMA Shin<br>of National Institute of Informatics/SOKENDAI |  |

| I TOTESSOL (                 | national institute of informatics/SOMENDAI                     |  |

| Subadvisor Dr. KATO Hiroyuki |                                                                |  |

| Professor of                 | of National Institute of Informatics/SOKENDAI                  |  |

| Examiner Dr.                 | TEI Kenji                                                      |  |

| Professor of                 | of Waseda University                                           |  |

| Examiner Dr.                 | ISHIKAWA Fuyuki                                                |  |

| Professor of                 | of National Institute of Informatics                           |  |

Examiner Dr. D'IPPOLITO Nicolás Professor of University of Buenos Aires

# Contents

| $\mathbf{Li}$ | st of                 | Figures xi                             |

|---------------|-----------------------|----------------------------------------|

| No            | otati                 | on in Figures xv                       |

| $\mathbf{Li}$ | st of                 | Tables xvii                            |

| $\mathbf{Li}$ | st of                 | Algorithms xix                         |

| Al            | ostra                 | ct xxi                                 |

| 1             | $\operatorname{Intr}$ | oduction 1                             |

|               | 1.1                   | Formal methods in software engineering |

|               | 1.2                   | Qualitative controller synthesis       |

|               | 1.3                   | Proposed approach                      |

|               | 1.4                   | Objectives                             |

|               | 1.5                   | Outline                                |

| <b>2</b>      | Sur                   | vey of Related Areas 7                 |

|               | 2.1                   | Supervisory control                    |

|               | 2.2                   | Reactive synthesis                     |

|               | 2.3                   | Automated planning                     |

| 3             | Bac                   | kground 13                             |

|               | 3.1                   | Event-based reactive systems 13        |

|               | 3.2                   | Labeled transition systems             |

|               | 3.3                   | Fluent linear temporal logic           |

|          | 3.4 | LTS control synthesis                                                                            | 17 |  |

|----------|-----|--------------------------------------------------------------------------------------------------|----|--|

|          | 3.5 | Parametric timed automata                                                                        | 19 |  |

|          | 3.6 | Satisfiability modulo theories                                                                   | 23 |  |

| 4        | Ind | ustrial Automation Example                                                                       | 25 |  |

| <b>5</b> | AG  | Qualitative Approach for Makespan                                                                |    |  |

|          | 5.1 | The main parts of the problem                                                                    | 29 |  |

|          | 5.2 | Defining makespan                                                                                | 31 |  |

|          | 5.3 | Measuring makespan                                                                               | 33 |  |

|          | 5.4 | Comparing makespan                                                                               | 35 |  |

|          | 5.5 | Dealing with contingencies                                                                       | 35 |  |

|          | 5.6 | Makespan-minimising controllers                                                                  | 37 |  |

|          | 5.7 | Obtaining makespan-minimising controllers                                                        | 38 |  |

| 6        | Con | trol Problems with Activities                                                                    | 41 |  |

|          | 6.1 | Industrial example as a control problem                                                          | 41 |  |

|          | 6.2 | Understanding time in LTS control                                                                | 44 |  |

|          | 6.3 | Modelling activities in LTSs                                                                     | 44 |  |

|          | 6.4 | Defining control problem with activities                                                         | 46 |  |

| 7        | ΑG  | ualitative Comparison Framework                                                                  | 49 |  |

|          | 7.1 | Comparing under the same contingencies $\ldots \ldots \ldots \ldots \ldots$                      | 49 |  |

|          | 7.2 | Timed semantics of LTS                                                                           | 52 |  |

|          | 7.3 | Using parameters to measure makespan                                                             | 56 |  |

|          | 7.4 | Comparing symbolic expressions                                                                   | 58 |  |

|          | 7.5 | Beyond the horizon                                                                               | 60 |  |

|          |     | 7.5.1 Motivating example $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 60 |  |

|          |     | 7.5.2 Interpreting the infinity in PTA                                                           | 62 |  |

| 8        | A N | Iakespan-Minimising Controller                                                                   | 67 |  |

|          | 8.1 | Defining makespan-minimising controllers                                                         | 67 |  |

|          | 8.2 | Synthesising makespan-minimising controllers                                                     | 70 |  |

#### Contents

| 9  | Eva   | luatio | n                                                              | <b>75</b> |

|----|-------|--------|----------------------------------------------------------------|-----------|

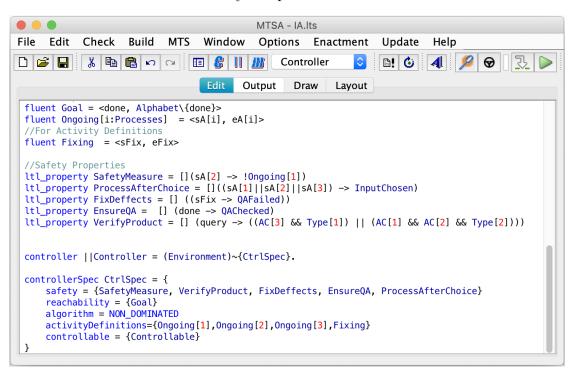

|    | 9.1   | Exten  | ding MTSA                                                      | 76        |

|    |       | 9.1.1  | MTSA                                                           | 76        |

|    |       | 9.1.2  | Specifying control problems with activities in MTSA $\ldots$ . | 79        |

|    |       | 9.1.3  | Implementing the comparison framework                          | 80        |

|    |       | 9.1.4  | Comparing $\Gamma$ expressions with Z3                         | 82        |

|    | 9.2   | Exper  | iments                                                         | 84        |

|    |       | 9.2.1  | Comparison against standard synthesis algorithm $\ldots$ .     | 84        |

|    |       | 9.2.2  | Scalability in the job scheduling example                      | 89        |

|    |       | 9.2.3  | Discussion                                                     | 90        |

| 10 | Rela  | ated W | Vork                                                           | 93        |

|    | 10.1  | Quant  | itative approaches for preferences                             | 93        |

|    | 10.2  | Qualit | ative approaches for preferences                               | 95        |

|    | 10.3  | Tempo  | oral problems and uncertainty                                  | 97        |

| 11 | Con   | clusio | ns                                                             | 101       |

|    | 11.1  | Contri | ibutions                                                       | 101       |

|    | 11.2  | Limita | ations and potential extensions                                | 102       |

| Bi | bliog | graphy |                                                                | 105       |

# List of Figures

| 2.1 | Control-loop system of a plant and its supervisor                                                                | 8  |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The interface of a controller for a coffee maker                                                                 | 10 |

| 3.1 | Generic example of parallel composition of two LTS                                                               | 15 |

| 3.2 | Examples of deterministic and non-deterministic LTSs                                                             | 16 |

| 3.3 | General example of timed automata.                                                                               | 19 |

| 3.4 | General examples of Parametric Timed Automata                                                                    | 21 |

| 3.5 | Timed automatons obtained by replacing the parameters of $H_1$ with                                              |    |

|     | the values indicated in each parameter valuation                                                                 | 22 |

| 4.1 | Illustration of an industrial automation plant with five tools and                                               |    |

|     | two types of input products to be processed                                                                      | 26 |

| 4.2 | Requirements of the industrial automation example in natural                                                     |    |

|     | language                                                                                                         | 26 |

| 4.3 | Industrial automation example activities                                                                         | 27 |

| 4.4 | Alternatives for using the tools on products of type two                                                         | 28 |

| 5.1 | Two main problems and its different components                                                                   | 30 |

| 5.2 | Satisfaction of safety $(\Box S)$ and reachability $(\Diamond P)$ goals over traces.                             | 31 |

| 5.3 | Makespan in reachability and safety controllers                                                                  | 32 |

| 5.4 | Using numbers to measure makespan                                                                                | 33 |

| 5.5 | Formalisms that are used in each step of the transformation to solve                                             |    |

|     | the problem of measuring qualitative makes<br>pan and comparing it. $% \left( {{{\bf{n}}_{{\rm{s}}}}} \right)$ . | 34 |

| 5.6 | Comparison of two controllers under different environment behaviour                                              |    |

|     | during the execution.                                                                                            | 36 |

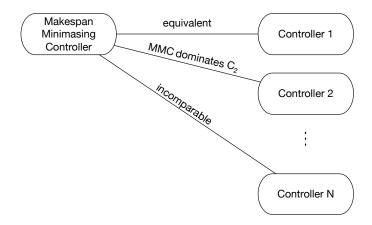

| 5.7 | Possible relations between a makespan-minimising controller and other controllers. | 38 |

|-----|------------------------------------------------------------------------------------|----|

| 5.8 | Proposed approach to synthesis a makespan-minimising controller                    | 39 |

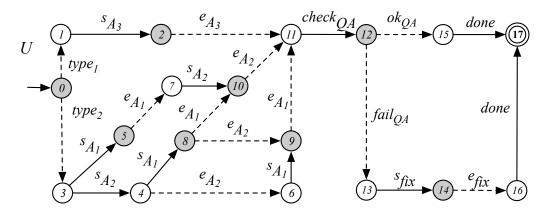

| 6.1 | LTS components describing the behaviour of the industrial automa-<br>tion example  | 42 |

| 6.2 | Production constraints described in FLTL.                                          | 42 |

| 6.3 | Fluent definitions used to describe the formulas of the automation                 | 14 |

| 0.0 | example                                                                            | 43 |

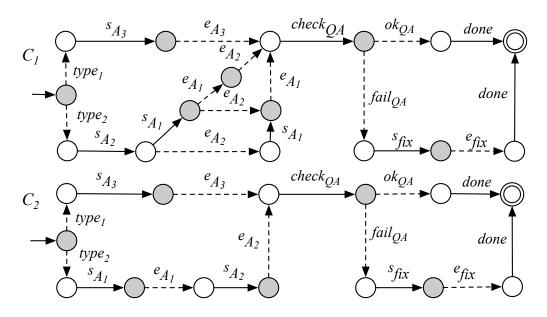

| 6.4 | Possible controllers for the same problem.                                         | 43 |

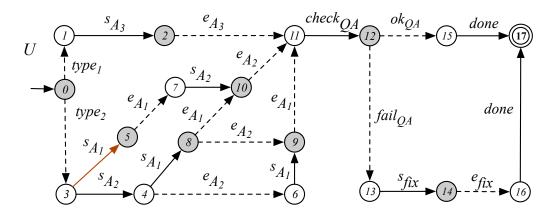

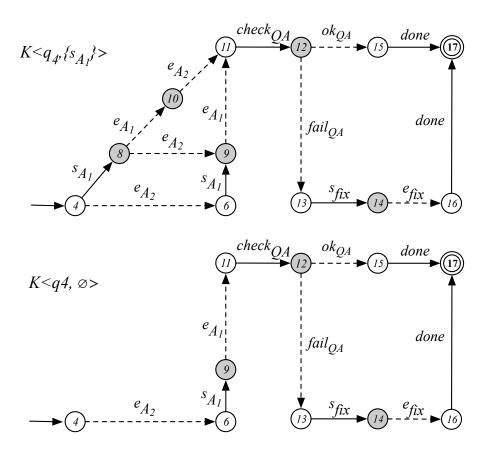

| 6.5 | Universal controller for the industrial example                                    | 48 |

| 7.1 | Scheduled composition of the controllers and environment from the                  |    |

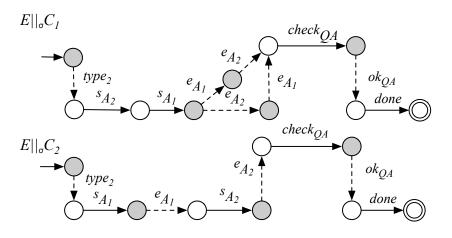

|     | industrial automation example                                                      | 53 |

| 7.2 | Timed semantics (PTAs) of the controllers and environment of the                   |    |

|     | industrial automation example                                                      | 55 |

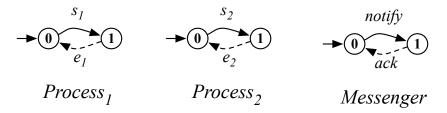

| 7.3 | Environment model of two process activities and one communication                  |    |

|     | process                                                                            | 60 |

| 7.4 | A possible controller executed with the environment satisfies the goal             | 61 |

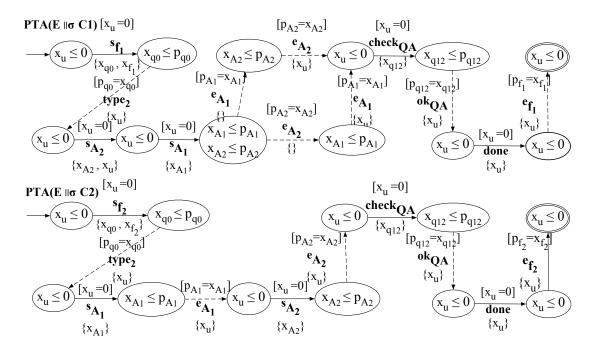

| 7.5 | Timed semantics of the controller of the two activities example                    | 62 |

| 7.6 | Interpreter automata of the controller of the two activities example               | 65 |

| 7.7 | Timed Automaton obtained after replacing the values of the Inter-                  |    |

|     | mediate PTA of the controller of the two activities example                        | 65 |

| 7.8 | PTA that does not accept $abd^*$ , when considering valuations over                |    |

|     | the reals                                                                          | 66 |

| 7.9 | Interpreting the infinity parameters valuation in a more general PTA               | 66 |

| 8.1 | Universal controller for the example of the industrial automation                  |    |

|     | example                                                                            | 71 |

| 8.2 | SubLTSs of the universal controller from the state $q_4$                           | 72 |

| 8.3 | SubLTSs of the universal controller from the state $q_3$                           | 73 |

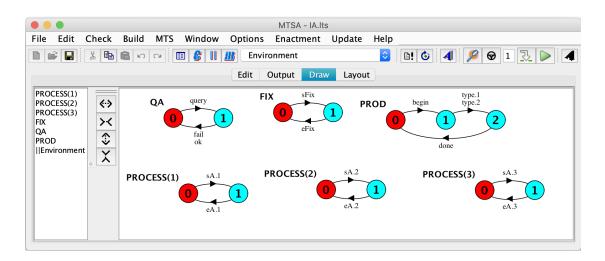

| 9.1 | Interface of MTSA displaying the specification of the industrial                   |    |

|     | automation example                                                                 | 77 |

| 9.2  | MTSA displaying the components of the environment of the indus-       |    |

|------|-----------------------------------------------------------------------|----|

|      | trial automation example.                                             | 78 |

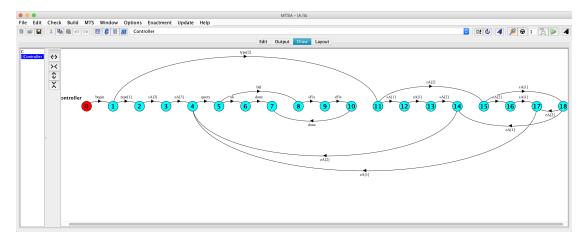

| 9.3  | Visualization of the controller synthesised by the standard synthesis |    |

|      | algorithm of MTSA.                                                    | 78 |

| 9.4  | Interface of MTSA displaying the lower part of the specification of   |    |

|      | the industrial automation example with the activities definition and  |    |

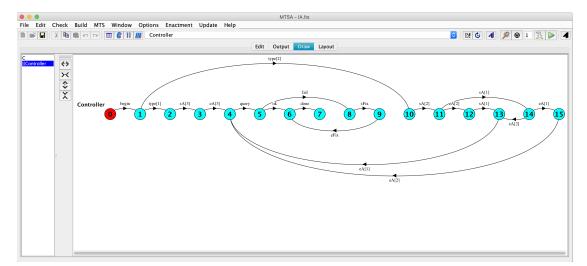

|      | a keyword to enable Algorithm 2                                       | 79 |

| 9.5  | Visualization of the controller synthesised by the Algorithm 2        | 80 |

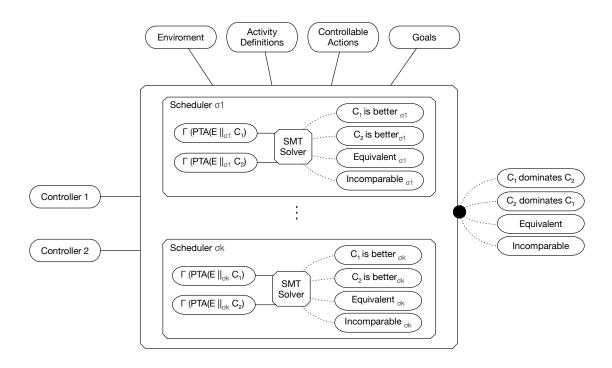

| 9.6  | Comparison framework for a pair of controllers $C_1$ and $C_2$        | 82 |

| 9.7  | Comparing two $\Gamma$ expressions with Z3                            | 83 |

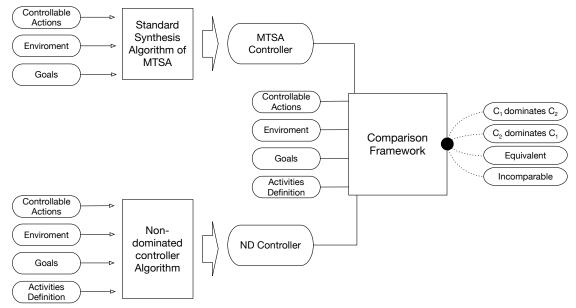

| 9.8  | Experimental setting to compare the solution generated by Algo-       |    |

|      | rithm 2 against the ones produced by standard synthesis algorithm     |    |

|      | of MTSA                                                               | 85 |

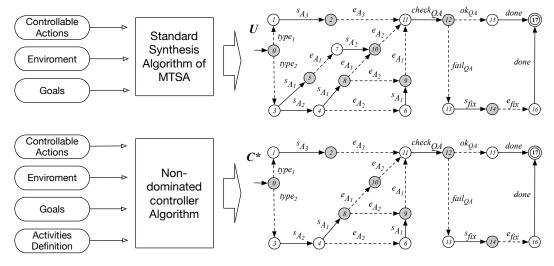

| 9.9  | Controllers produced by standard algorithm of MTSA and Algorithm 2.   | 87 |

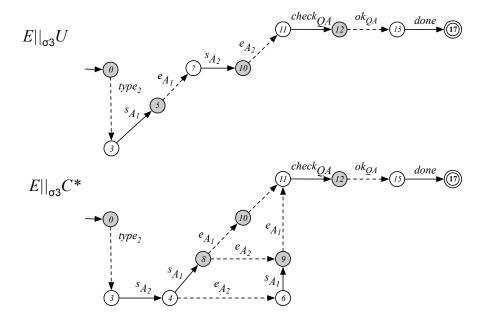

| 9.10 | Scheduled parallel composition of controllers generated by the        |    |

|      | standard synthesis algorithm and the Algorithm 2 on the IA example.   | 88 |

## Notation in Figures

- $\longrightarrow$  transition or controllable transition (in a control problem setting)

- $-{\twoheadrightarrow}$  uncontrollable transition

- $\underline{a}$  transition with action a

- $\xrightarrow{[x==10]}{a} \text{ transition with action } a \text{ and guard } [x==10]$

- $\overrightarrow{\{x\}} \text{ transition with reset clocks } \{x\}$

- $\bigcirc$  state or transient states (when non-transient states are distinguished)

- non-transient state

- $\bigcirc$  final state or goal state (in a control problem setting)

- $x \le 10$  state with invariant  $x \le 10$

# List of Tables

| 6.1 | Activities definition for the industrial automation example                | 45 |

|-----|----------------------------------------------------------------------------|----|

| 7.1 | Possible results of comparing two controllers                              | 59 |

| 9.1 | Possible results of comparing two controllers under a scheduler $\sigma$ . | 81 |

| 9.2 | Results of the evaluation of Algorithm 2 on cases studies from             |    |

|     | different fields that involve the execution of activities to reach a goal. | 86 |

| 9.3 | Results of the performance of Algorithm $2$ on the JOB case study          |    |

|     | with increasing number of tasks                                            | 90 |

|     |                                                                            |    |

# List of Algorithms

| 1 | Obtaining $\Gamma$ of the timed semantics of a controller | 57 |

|---|-----------------------------------------------------------|----|

| 2 | Non-dominated controller algorithm.                       | 70 |

### Abstract

Qualitative controller synthesis techniques produce controllers that guarantee to achieve a given goal in the presence of an adversarial environment. However, qualitative synthesis only produces one controller out of many possible solutions and typically does not provide support for expressing preferences over other alternatives.

Synthesis and planning techniques that allow expressing preferences exist, such as those regarding performance or reliability. Such quality attributes are modelled by introducing a quantitative aspect to the system specification, which imposes a preference order on the controllers that satisfy the qualitative part of the specification. However, from a practical perspective, these approaches require modelling quality attributes quantitatively, whereas in many cases, such detailed representation is not available, possible, or desired.

The main objective of this thesis is to present a formal approach to reason about preferences qualitatively, restricting attention to makespan of discrete event-based controllers for safety and reachability goals. Time is reasoned upon symbolically, which relieves the user from providing concrete quantitative measures. In particular, we study the scenario in which durations of individual activities are not known up-front.

First, we show how controllers can be symbolically and fairly compared by fixing the contingencies. Then, we present an algorithm to produce controllers that are makespan-minimising. The algorithm was implemented in the MTSA tool, as well as evaluated in case studies.

**Keywords:** Discrete Event Systems, Reactive Synthesis, Supervisory Control, Reachability, Makespan.

# Introduction

#### 1.1 Formal methods in software engineering

Specifying the requirements of the system is one of the first steps in the process of constructing a system [1]. In this process, the assumptions about the environment in which the system will be deployed are defined, as well as the guarantees that the system will provide. In software engineering, the requirements are divided into functional requirements and non-functional requirements. Functional requirements are intended to capture the behaviour that the system must have, while non-functional requirements describe quality attributes of the system, which define a preference order among possible solutions.

Modelling is a key part in the process of building a system. Models are used to build abstractions of the environment based on our assumptions and understanding of the world. These models are used to represent the behaviour of the system that we intend to build. Besides, models are useful to validate those abstractions and assumptions with relevant stakeholders and engineers. In particular, we are interested in using mathematical models to describe the behaviour of both the environment and the system, because this enables the possibility of formally checking if our system is correct with respect to the specification. In addition, this type of models can be executed by a machine, reducing the gap between models and what it is executed.

In a world with constantly increasing interaction between systems and humans, the attention to techniques that can ensure the satisfaction of the requirements is rising. For instance, Model checking [2] is becoming a key instrument in critical systems such as flying control systems [3, 4], industrial robot systems [5], autonomous driving [6, 7], and medical systems [8]. Model checking is a technique that allows us to verify that our system satisfies the requirements if we specify them in a formal language, which means that we can automatically check that our system is correct according to the specification.

In this thesis, we are interested in modelling problems that involve reactive systems. Reactive systems [9] are computing systems which are interactive in nature. Their interaction could be with other computing systems and also with human beings. From the reactive system point of view, all these are external interactions with its environment. Reactive systems are among the hardest computing systems to program [10], because this type of systems needs to be prepared to react to any possible interaction with the environment that is defined by its interface.

Temporal logic [56] is a formalism that has shown to produce good results in specifying functional requirements of reactive systems [10]. By using this technique, we can specify the requirements in a formal language that clearly distinguishes the assumptions and guarantees of our system. One of the advantages of specifying our system in a formal language like temporal logic is that we can directly apply model checking techniques.

Specifying requirements in a formal language like temporal logic also enables a more ambitious goal, which is building solutions from the specification automatically. Given a specification in terms of assumptions and guarantees, discrete controller synthesis is a technique that can produce solutions that are correct by construction regarding the specification [11, 12]. General synthesis from temporal logic is known to be 2EXPTIME-complete [11]. However, there are polynomial algorithms for a subset of this logic. For instance, there are applications of synthesis to robotic problems [13, 14, 15] that are specified with GR(1) formulas [16], which are a subset of linear temporal logic formulas that have polynomial synthesis algorithms.

Controllers can be synthesised offline and executed at run-time. This means that synthesis time is not a critical aspect, but termination is. Once a controller is synthesised, it is expected to be executed a large number of times. It will only be necessary to synthesise a new controller when changes in the environment or requirements arise. In these cases, updating controller techniques could be applied [17], which, however, is not within the scope of this work.

#### **1.2** Qualitative controller synthesis

The problem of automatically synthesising event-based solutions from environment models and qualitative goal specifications has been widely studied [18, 11, 19, 16]. In these problems, the environment and the goals are specified by using a formal language. The environment is typically modelled as a state machine whose actions are partitioned into controllable and uncontrollable actions. The controller synthesis problem is to automatically produce a solution, i.e., a controller, that by only disabling controllable actions guarantees the satisfaction of the goals. In particular, we focus on reachability and safety goals which are of interest to supervisory control theory [18], conformant [20] and contingent [21] planning.

Qualitative control problems are boolean in the sense that a controller satisfies a set of goals, or it does not. When a qualitative control problem has a solution, we say it is realisable. Realisable control problems may allow for several possible solutions. Different solutions may differ in the strategy which they apply to satisfy the goals. Typically, based on the arrival of monitored actions, the strategies implemented by controllers decide which and when to start activities. For instance, regarding end-to-end makespan, a controller that starts several activities concurrently instead of executing them sequentially can be, intuitively, considered as a better strategy, no matter which the durations of the activities are. Unfortunately, qualitative synthesis procedures are, so far, oblivious to such considerations. The controller produced is one of the many alternatives and users cannot specify their preferences; e.g., lower-makespan controller. Thus, it is desired to have the ability to express preferences and automatically compute a solution from a set of possible solutions to a control problem accordingly.

Synthesis and planning techniques that allow expressing preferences exist, such as those regarding performance or reliability. Such quality attributes are modelled by introducing a quantitative aspect to the system specification, which imposes a preference order on the controllers that satisfy the qualitative part of the specification [22, 23, 24]. However, from a practical perspective, these approaches require modelling quality attributes quantitatively, whereas in many cases, such detailed representation is not available, possible, or desired.

#### 1.3 Proposed approach

In this thesis, we define lower-makespan as our preference and introduce a formal approach to qualitatively reason about makespan of discrete event-based controllers for safety and reachability goals. To reason qualitatively about makespan of controllers, we introduce a symbolic time metric derived from Parametric Timed Automata (PTA) [25] semantics. This metric requires modelling sub-tasks of the problem which take time as activities, but no quantitative information about the duration of the activities is required. Then, we define a mechanism to compare makespan of controllers under unknown durations of activities and event contingencies produced by uncontrollable behaviour. Such a comparison is made through exhaustive analysis by using a symbolic computation over the parameters of a PTA [26] and Satisfiability Modulo Theories (SMT) solving [27]). The parameters of the PTA represent the uncertain duration of the activities. Then, we define makespan-minimising controllers by using the symbolic comparison and we introduce an algorithm that produces a makespan-minimising controller qualitatively. The algorithm is implemented in the MTSA tool [28] and evaluated in case studies. The evaluation consists of comparing the output produced by our algorithm against the standard synthesis algorithm of the tool.

#### 1.4 Objectives

The main objective is to present a formal approach to reason about preferences qualitatively, restricting attention to makespan of discrete event-based controllers for safety and reachability goals. We aim to provide a framework in which time is reasoned symbolically, which relieves the user from providing concrete quantitative measures. In particular, we study the scenario in which durations of individual activities are not known up-front. Our hypothesis is that it is possible to i) define a qualitative framework to compare controllers qualitatively regarding their makespan, ii) specify preferences in control problems qualitatively, and iii) produce controllers that reflect those preferences.

The intended output of this thesis is a qualitative framework to compare of makespan of controllers, and a qualitative algorithm that produces controllers with lower-makespan than the ones produced by standard qualitative synthesis algorithms. To validate our approach we provide formal definitions and proofs to show why reasoning about preferences by using our formalisation is valid. Besides, we implement our ideas in the MTSA tool [28], a qualitative synthesis tool, and compare the controllers produced by our algorithm against the ones produced by the tool.

#### 1.5 Outline

This thesis is structured as follows. Chapter 2 surveys the main related areas. Chapter 3 introduces the background. Chapter 4 illustrates an example that is used throughout the rest of the thesis. Chapter 5 presents the general problem and the approach of this work. Chapter 6 introduces the control problem with activities, and it models the example as a control problem. Chapter 7 defines how to compare the makespan of a pair of discrete controllers qualitatively. Chapter 8 defines makespan-minimising controllers and presents an algorithm that produces a makespan-minimising controller. Chapter 9 shows the experimental results of the implementation of the algorithm in case studies. Chapter 10 discusses about the related work. Chapter 11 presents the conclusions, limitations of the proposed approach and future directions.

# 2 Survey of Related Areas

The problem of automatically producing solutions from formal specification has a long history. The first formulation of the problem was done by Church [29, 30] in the context of logical circuits. Church introduced the problem of synthesizing digital circuits, which have inputs and outputs signals, from logical specifications. Different communities proposed variations of this problem, as well as formulations and approaches that aim to solve the problem of automatically producing solutions from formal specification. Some of the research areas that tackled a similar problem are *supervisory control* [18] in control engineering community, *reactive synthesis* [11] in computer science community and *automated planning* [31] in artificial intelligence community. In the recent years, there are several works that are attempting to connect all these approaches to bring the knowledge gained in one community to the others [12, 32, 33, 34, 35, 36, 37, 38]. There are authors that are proposing unified views of some forms of automated planning and reactive synthesis [33] because of the similarities between these areas. Some examples of knowledge exchange between these communities are the use of planning heuristics to obtain solutions in the supervisory control community [39], and the use of LTL to model temporally extended goals in the planning community [40, 41, 42].

#### 2.1 Supervisory control

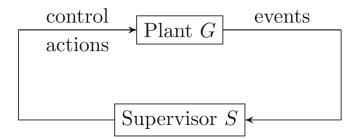

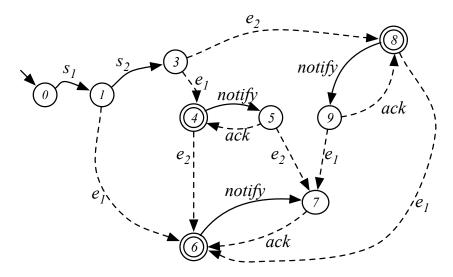

Supervisory control [18] problems of discrete-event systems are defined as a plant, a set of controllable actions and a set of marked states. The plant is typically modelled as a deterministic finite-state automata. As defined in this thesis, the actions of the automata are partitioned into controllable and uncontrollable actions. The marked states are a subset of states of the automata, which are the acceptance ones. The solution to this problem is a supervisor, which must guarantee achieving the marked states by disabling controllable actions. A supervisor is defined as a function that enables a subset of events based on the history of events that have happened so far. The subset of actions must include all the uncontrollable actions because the supervisor has no control over them. The supervisor and the plant form a closed-loop system, in which the supervisor chooses the control actions from the possible events enabled by the plant. Figure 2.1 illustrates the control-loop system. Then, the plant executes one of the actions enabled by the supervisor. However, the supervisor has no control over this choice.

Figure 2.1: Control-loop system of a plant and its supervisor [12].

A supervisor is *non-blocking* if it can reach a marked state from any reachable state of the closed-loop system formed by the supervisor and the plant [12]. This means that the control-loop system never reaches a deadlock, unless it is a marked state, or never reaches a livelock that does not contain marked states. A typical requirement for supervisors is maximal permissiveness. This means that a supervisor is expected to disturb the plant as little as possible. A unique maximally-permissive supervisor always exist, which is not generally the case in the reactive synthesis framework [12].

The problems presented in this work are similar to the ones of supervisory control when the plant is fully observable. In fully observable problems, the supervisor can observe all the events that happened and determine the current event of the plant uniquely, because the plant is deterministic.

#### 2.2 Reactive synthesis

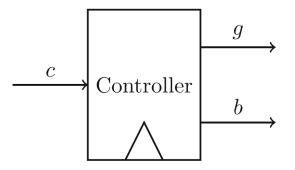

The reactive synthesis problem was introduced by Pnueli and Rosner in 1989 [11] by using linear temporal logic (LTL) [43] as the specification language for both the environment and the system goals. The propositions used to describe those formulas are partitioned into two disjoint sets: the input (uncontrollable) propositions and the output (controllable) propositions. A solution to this problem is a controller, which is an operational specification of a module that restricts the traces allowed in the specification of the environment to those traces satisfying the system goals. Controllers are open dynamical systems in the sense that its behaviour depends on the inputs that it receives. A reactive system has to satisfy a specification for every possible input to the system. The specification of reactive synthesis problems is considered to be more declarative, because it describes the desired behaviour of the controller on the interface level without setting requirements about the internal structure of the solution [12]. Figure 2.2 illustrates an example of a typical controller with one input and two outputs.

Classical definition of reactive synthesis does not have a notion of plant or environment modelled as state machine [44, 11]. However, in the controller synthesis community, there are variations of the original formulation that use plants to describe the behaviour of the environment [45, 46, 47, 48]. In these works, the interaction between the controller and the plant (environment) is done through events as in supervisory control problems. This is also the approach taken in this thesis. One advantage of modelling the environment as an automata is to reduce the size of the formulas used in the specification. This is important because translating an LTL formula into an automata is at least exponential in the size of the formula [12, 11].

Figure 2.2: The interface of a controller for a coffee maker [12]. Input signal c is the button to order coffee. Output signals are grinding g and brewing b.

Solving a reactive synthesis problem typically involves transformations from LTL formulas into some type of word automaton such as Büchi automaton [12]. Then, the automaton is usually translated into a game between two players: the environment and the system. In this game, the system has to be able to win the game for every possible play of the environment [48]. If this is possible, there is a winning strategy, the problem is realisable and there is a controller.

The general problem of synthesis from LTL specifications was shown to be 2EXPTIME complete [11]. Thus, the reactive synthesis community focused on exploring subsets of LTL formulas that are expressive enough to describe interesting problems. For instance, GR(1) formulas are one of the most expressive and widespread formulas with polynomial synthesis algorithms [16].

#### 2.3 Automated planning

Planning problems are typically defined as a finite set of propositions that can be modified by the use of actions [31]. Actions have preconditions and effects. The preconditions are the values that the propositions must hold to apply an action, while the effects define how the values of the propositions change. The goal is to generate a sequence of actions that modifies the propositions from their initial values to the goal values, which are called the goal propositions. This can also be represented as a set of states, actions, and transitions, where each state represents a different valuation of the propositions. In this representation, the goal states are those that represent the values of the goal propositions. A plan, the solution, is a sequence of actions leading from the initial state to a goal state. Planning domains and problems are sometimes described in PDDL (planning domain definition languange) [49].

In classical planning problems, the effects of the actions are deterministic, which means that all the actions are controllable. The reactivity of the environment is typically not modelled, and in case of differences between the plan and the execution, the most common approach is to re-plan, i.e., to produce a new plan. Thus, the focus of this area is to produce efficient and optimal algorithms to generate plans. Efficiency is measured in time to produce the solution, and optimality typically refers to the number of actions of the plan. More compact plans are preferable. In this type of problems, heuristic search [50] is the approach that is often used to find a solution.

The use of temporal logics to specify problems is not limited to the reactive synthesis community. The planning community has also introduced the use of LTL to model temporally extended goals [51] for planning domains that have actions with both deterministic and non-deterministic effects. Most of the approaches propose to compile LTL specifications into classical planning [41, 42], while others propose specific planners for problems with LTL goals [40].

Planning domains with non-deterministic actions exist [52, 53] but with less attention than its deterministic counterpart. Fully Observable Non-Deterministic (FOND) Planning [54] models non-determinism by defining a set of propositions whose value can change over time regarding actions with non-deterministic effects. This makes FOND problems similar to reactive synthesis problems because the exact plan that will be executed is not known until execution time. Thus, FOND plans have to consider all possible contingencies that may appear during execution. Strong plans are those that guarantee that the goal is achieved regardless of contingencies. In the recent years, it has been shown that it is possible to transform reactive synthesis problems with reachability and safety goals into FOND planning problems [55].

# 3 Background

In this chapter we present the key underlying theories that are necessary to explain the rest of this work. Section 3.1 briefly introduces the concept of reactive systems. Section 3.2 and Section 3.3 describe the formalisms that are used to define control problems in Section 3.4. Section 3.5 and Section 3.6 presents the formalisms that are used to define the comparison between two LTS controllers.

#### 3.1 Event-based reactive systems

Reactive systems [9] are machines that interact with their environment through sensors and actuators. This type of systems can modify the environment through their actions and perceive the changes through their sensors. The interaction between a reactive system and the environment is modelled by events (or actions). *Act* is a set of symbols that defines the set of observable actions. Some of these actions are executed by the machine, while other actions are events that the machine observes to decide its next actions. Both the environment and the machine (the controller) will be modelled by using Labelled Transition Systems, which are defined in the next section.

#### 3.2 Labeled transition systems

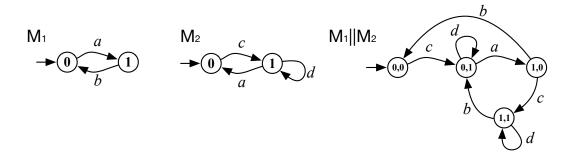

Labelled Transition System (LTS) [56] are one of the formalisms that is typically used for modelling the behaviour of a system. LTS is a transition system in which states are connected through transitions, which are labelled with actions. By using LTS for modelling behaviour, it is possible to decompose the behaviour of the system into several components. The interaction between these components (LTSs) is modelled by the parallel composition [56] of the LTSs. The parallel composition is defined as an LTS that models the asynchronous execution of composed models, interleaving non-shared actions while forcing synchronisation on shared actions. We use  $q \xrightarrow{\ell} q'$  to denote a transition that  $(q, \ell, q') \in \Delta$ . Figure 3.1 illustrates two different LTSs and the parallel composition of them.

**Definition 3.1 (Labelled Transition Systems)** A labelled transition system (LTS) is a tuple  $(Q, \Sigma, \Delta, q_0)$  where

- Q is a finite set of states,

- $\Sigma \subseteq Act$  is its alphabet, Act is the set of observable actions,

- $\Delta \subseteq (Q \times \Sigma \times Q)$  is a transition relation, and

- $q_0 \in Q$  is the initial state.

**Definition 3.2 (Parallel Composition)** The parallel composition (||) of two LTSs M and N, is a symmetric operator such that  $M||N = (Q_M \times Q_N, \Sigma_M \cup \Sigma_N, \Delta_{M||N}, (q_{M_0}, q_{N_0}))$ , where  $\Delta_{M||N}$  is the smallest relation that satisfies the following rules:

$$\frac{q_M \xrightarrow{\ell}_M q_M'}{(q_M, q_N) \xrightarrow{\ell}_{M \parallel N} (q_M', q_N)} \ell \in \Sigma_M \setminus \Sigma_N \xrightarrow{q_N \xrightarrow{\ell}_N q_N'}{(q_M, q_N) \xrightarrow{\ell}_{M \parallel N} (q_M, q_N')} \ell \in \Sigma_N \setminus \Sigma_M$$

$$\frac{q_M \xrightarrow{\ell}_M q_M', \ q_N, \xrightarrow{\ell}_{N, q_N'}}{(q_M, q_N) \xrightarrow{\ell}_{M \parallel N} (q_M', q_N')} \ell \in \Sigma_M \cap \Sigma_N$$

Figure 3.1: Generic example of parallel composition of two LTS.

The *paths* and *traces* of an LTS are used to describe possible behaviour during the execution. A path of an LTS is a possibly infinite sequence of states and actions, i.e., a valid sequence of transitions in the LTS. A trace is a sequence of actions that can be executed by the LTS. That is, that there exists a corresponding path in the LTS. We denote the set of infinite traces of an LTS M as Tr(M). The satisfaction of a formula in the LTS will be determined by its traces. The details will be explained in the next section. We also refer to the possibly infinite set of paths of an LTS that reach a state q from the initial state as Paths(M,q). For example:  $q_0 \xrightarrow{a} q_1 \in Paths(M_1, q_1)$  and  $q_0 \xrightarrow{c} q_1 \xrightarrow{d} q_1 \in Paths(M_2, q_1)$ . Note that  $q_{0,0} \xrightarrow{a} q_{0,1} \notin Paths(M_1 || M_2, q_{0,1})$  because the parallel composition synchronizes on the shared action a.

**Definition 3.3 (Path)** A path  $q_0 \xrightarrow{\ell_0} q_1 \xrightarrow{\ell_1} \dots$  of an LTS  $M = (Q, \Sigma, \Delta, q_0)$  is a sequence of transitions of an LTS M.

**Definition 3.4 (Trace)** A trace of an LTS  $M = (Q, \Sigma, \Delta, q_0)$  is a sequence of actions  $\pi = \ell_0, \ell_1, \ldots$ , iff there exists a path  $q_0 \xrightarrow{\ell_0} q_1 \xrightarrow{\ell_1} \ldots$  in the LTS M.

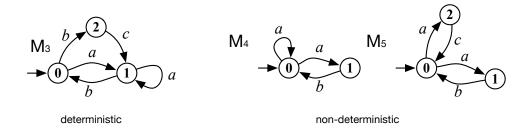

LTS models can be deterministic or non-deterministic. A model is *deterministic* when given a state and an action of an LTS there is at most one successor. This means that given a trace there is a unique corresponding path. In contrast, if an LTS is *non-deterministic*, given a trace there may be multiple corresponding paths, because for a given action a state may have more than one successor. This work focuses only on deterministic models. Figure 3.2 illustrates some examples of deterministic and non-deterministic LTSs.

Figure 3.2: Examples of deterministic and non-deterministic LTSs.

**Definition 3.5 (Deterministic)** An LTS  $(Q, \Sigma, \Delta, q_0)$  is deterministic when  $\forall q \in Q \ \forall \ell \in \Sigma \ \{(q, \ell, q') \mid (q, \ell, q') \in \Delta\} \le 1.$

We overload the symbol of the transition relation to define the set *enabled* actions in a state as  $\Delta(q) = \{\ell \mid q \stackrel{\ell}{\to} q'\}$ , and the successors of a state as  $\Delta(q, \ell) = \{q' \mid q \stackrel{\ell}{\to} q'\}$ . For example, in the LTS  $M_3$ ,  $\Delta(q_0) = \{a, b\}$  and  $\Delta(q_0, a) = \{q_1\}$ . Besides, when members of a tuple are not explicitly described we assume them to be indexed by the name of the tuple. For instance, given an LTS M we refer to its members as  $M = (Q_M, \Sigma_M, \Delta_M, q_{M_0})$  with  $q_M$  a state of  $Q_M$ .

#### **3.3** Fluent linear temporal logic

Temporal logic [56] is one of the most commonly used formalism to express properties about correctness of the execution of a system. This logic extends propositional logic with modalities that permit to describe infinite behaviour that a system must have. Temporal logics can be linear or branching, depending on how time is modelled. From a linear-time perspective there is only one possible future, while from a branching-time perspective multiple alternative futures may exist at the same time. That is to say, branching logic can describe properties that may only hold in some futures, while linear logic describes properties that must hold in every possible future. This work uses an extension of Linear Temporal Logic (LTL) [56], which is the logic that it is used to describe linear-time properties.

Fluent Linear Temporal Logic (FLTL) [57] is the language that we use for describing properties. FLTL is a linear-time temporal logic for reasoning about fluents instead of state-based propositions. A *fluent Fl* is defined by a pair of sets

and a Boolean value:  $Fl = \langle I_{Fl}, T_{Fl}, Init_{Fl} \rangle$ , where  $I_{Fl} \subseteq Act$  is the set of initiating actions,  $T_{Fl} \subseteq Act$  is the set of terminating actions and  $I_{Fl} \cap T_{Fl} = \emptyset$ . A fluent may be initially *true* or *false* as indicated by  $Init_{Fl}$ . Every action  $\ell \in Act$  induces a fluent, namely  $\dot{\ell} = \langle \ell, Act \setminus \{\ell\}, false \rangle$ . The logic has the same expressiveness as standard LTL. However, as fluents can be used to overlay state-based propositions on an event-based model, FLTL allows to represent properties in a more compact manner.

Let  $\mathcal{F}$  be the set of all possible fluents over the observable actions *Act*. An FLTL formula is defined inductively by using the standard Boolean connectives and temporal operators **X** (next), **U** (strong until) as follows:

$$\varphi ::= Fl \mid \neg \varphi \mid \varphi \lor \psi \mid \mathbf{X}\varphi \mid \varphi \mathbf{U}\psi$$

where  $Fl \in \mathcal{F}$ , and  $\psi$  and  $\varphi$  are formulas FLTL. As well, we use the standard operators  $\wedge$ ,  $\diamond$  (eventually),  $\Box$  (always), and **W** (weak until). FLTL formula satisfaction is standard and it is computed over traces and fluents.

Let  $\Pi$  be the set of infinite traces over *Act*. The trace  $\pi = \ell_0, \ell_1, \ldots$  satisfies a fluent *Fl* at position *i*, denoted  $\pi, i \models Fl$ , if and only if one of the following conditions holds:

-  $Init_{Fl} \land (\forall j \in \mathbb{N} \cdot 0 \le j \le i \to \ell_j \notin T_{Fl})$

$- \exists j \in \mathbb{N} \cdot (j \leq i \land \ell_j \in I_{Fl}) \land (\forall k \in \mathbb{N} \cdot j < k \leq i \rightarrow \ell_k \notin T_{Fl})$

In other words, a fluent holds at position i if and only if it initially holds or some initiating action has occurred, but no terminating action has yet occurred. We denote that a possibly infinite trace  $\pi$  satisfies an FLTL formula  $\varphi$  for every position i as  $\pi \models \varphi$ .

#### 3.4 LTS control synthesis

The controller synthesis problem is the problem of automatically producing a solution from a formal specification. The solution to this problem is called a controller. The LTS control problem is an event-based control problem following the world-machine model [58]. In LTS control problems, the formal specification of the problem is decomposed into a description of the environment and a set of

functional goals [59]. The behaviour of the environment is described as an LTS (or the composition of several LTSs), and the goals are expressed as FLTL formulas. The environment describes when different actions can occur. The controller can decide when to execute some of these actions, but cannot control when the other actions happen. Thus, the actions  $\Sigma$  of the environment are partitioned into controllable actions  $\Sigma_c$  and uncontrollable actions  $\Sigma_u$  ( $\Sigma = \Sigma_c \cup \Sigma_u \land \Sigma_c \cap \Sigma_u = \emptyset$ ). When describing LTS models we may assume that this partition exists.

The controller is also modelled as an LTS that restricts the ocurrence of controllable actions based on the observation of the events that have occurred. A controller C is executed concurrently with the environment E. Since both of them are LTSs, this is modelled by the parallel composition of LTSs (E||C). To be a solution, a controller must satisfy the following conditions. First, a controller must ensure that the goals G are satisfied in every trace of its concurrent execution with the environment. We denote that a controller satisfies the goals as  $E||C| \models G$ , which means that every trace in the concurrent execution  $(\forall \pi \in Tr(E||C))$  satisfies the goals  $(\pi \models G)$ . Second, a controller must not block the uncontrollable behaviour. The notion of a controller that does not block uncontrollable actions is built on the concept of the *legal environment* for Interface Automata [60]. Intuitively, a controller C is a legal LTS for the environment E, when in every state  $(q_E, q_C)$  of E||C, an uncontrollable action is enabled in  $(q_E, q_C)$  iff it is also enabled in  $q_E$ . Third, the concurrent execution E||C| must be deadlock-free.

**Definition 3.6 (LTS Control Problem)** Given an LTS  $E = (Q_E, \Sigma, \Delta_E, q_{E_0})$ , a goal G expressed in FLTL, and a set of controllable actions  $\Sigma_c \subseteq \Sigma$ , the solution to the control problem  $\mathcal{E} = \langle E, G, \Sigma_c \rangle$  is to find a deterministic LTS  $C = (Q_C, \Sigma, \Delta_C, q_{C_0})$  such that i) C is a legal LTS for E, ii) E ||C| is deadlock free, and iii) every infinite trace  $\pi$  in Tr(E||C) satisfies G ( $\pi \models G$ ).

**Definition 3.7 (Legal LTS)** Given an LTS  $E = (Q_E, \Sigma, \Delta_E, q_{E_0})$ , an LTS  $C = (Q_C, \Sigma, \Delta_C, q_{C_0})$  and  $\Sigma_u \subseteq \Sigma$ , the LTS C is a legal LTS for E if  $\forall (q_E, q_C) \in Q_{E||C}$  holds that  $\Delta_{E||C}((q_E, q_C)) \cap \Sigma_u = \Delta_E(q_E) \cap \Sigma_u$ , where  $Q_{E||C}$  are the states of E||C.

To distinguish between *enabled controllable actions* and *enabled uncontrollable actions* we use the following notation.

- Enabled Controllable Actions:  $\Delta^c(q) = \Delta(q) \cap \Sigma_c$ .

- Enabled Uncontrollable Actions:  $\Delta^u(q) = \Delta(q) \cap \Sigma_u$ .

#### **3.5** Parametric timed automata

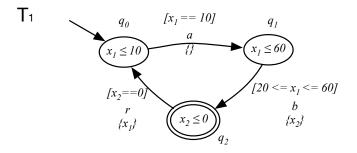

The formalisms mentioned above permit to describe properties about the behaviour of a system. However, by using those formalisms it is not possible to describe timing aspects. For instance, we are not able to model that an activity must finish within sixty seconds. Timed automata (TA) [56] is typically the formalism that is used to model the behaviour of time-critical systems. In fact, both LTS and TA are types of transition systems. The main difference is that TA comes with a finite set of clocks, which are real-valued variables. Note that this real-valued variables are used to represent time. Thus, in the transitions, clocks can be reset but cannot be assigned with a particular value. These clocks can be used to define time conditions in the automata. Conditions can be used to express invariants in the states or to describe guards in the transitions. That is to say, it permits to model conditions that the clocks of the system must satisfy to stay in a state or to transition from one state to another. For example, we could have a clock  $x_1$  to measure when an activity is being performed. Then, we could use a state invariant  $x_1 \leq 60$  to model that the activity must leave a state within sixty seconds, or a guard describing that some transition could only be taken within some time range  $20 \le x_1 \le 60$ . Automaton  $T_1$  of Figure 3.3 describes a timed automaton with some of these conditions.

Figure 3.3: General example of timed automata.

**Definition 3.8 (Timed Automaton)** A timed automaton (*TA*) is a tuple *TA* =  $(\Sigma, Q, Q_0, X, Q_f, I, \Theta)$  where

- $\Sigma$  is a set of actions,

- Q is a set of states,

- $Q_0 \subseteq Q$  is a set of initial states,

- X is a finite set of clocks with domain  $\mathbb{R}_{\geq 0}$ ,

- $Q_f \subseteq Q$  a set of final states

- $I: Q \to XC(X)$  a state-invariant function, and

- $\Theta$  is a set of edges s.t. each edge is a tuple  $(q_1, \ell, q_2, \lambda, \mu) \in \Theta$  with  $q_1 \in Q$ ,  $\ell \in \Sigma$ ,  $q_2 \in Q$ , a set of clocks to be reset  $\lambda \subseteq X$ , and a guard  $\mu \in XC(X)$ .

Conditions over clocks are usually referred as *clock constraints*. A valid clock constraint over the set of clocks X is defined as follows:

$$xc ::= x < r \mid x \le r \mid x \ge r \mid x > r \mid xc \land xc$$

where  $x \in X$  and  $r \in \mathbb{R}_{\geq 0}$ . We will refer to the set of clock constraints over a set of clocks X as XC(X).

Timed automata is very powerful formalism to model time-critical systems, but it requires to have the precise time constraints that the system must satisfy. In this work, we are going to use time models to give a time semantic to models in which the time constraints are not available upfront. Therefore, we are going to use *parametric timed automata* (PTA) [25] to give a time semantic to LTS models. Parametric timed automata is an extension of timed automata in which *clock constraints* can be also defined over a finite set of *parameters* P with domain  $\mathbb{R}_{\geq 0}$ . For instance, we would be able to express that an activity must finish within time p, where p could be any real value. This is essential for us to model that an activity may take some time in an abstract way. Similarly to PTA, a valid clock constraint over the set of clocks X and parameters P is defined as follows:

$$xc ::= x < r \mid x \le r \mid x \ge r \mid x > r \mid x p \mid xc \land xc$$

where  $x \in X$ ,  $p \in P$  and  $r \in \mathbb{R}_{\geq 0}$ . We will refer to the set of clock constraints over a set of clocks X as XC(X, P).

**Definition 3.9 (Parametric Timed Automaton)** A parametric timed automaton (*PTA*) is a tuple  $H = (\Sigma, Q, Q_0, X, P, Q_f, I, \Theta)$  where

- $\Sigma$  is a set of actions,

- Q is a set of states,

- $Q_0 \subseteq Q$  is a set of initial states,

- X is a finite set of clocks with domain  $\mathbb{R}_{\geq 0}$ ,

- P is a finite set of parameters with domain  $\mathbb{R}_{>0}$ ,

- $Q_f \subseteq Q$  a set of final states,

- $I: Q \to XC(X, P)$  a state-invariant function, and

- $\Theta$  is a set of edges s.t. each edge is a tuple  $(q_1, \ell, q_2, \lambda, \mu) \in \Theta$  with  $q_1 \in Q$ ,  $\ell \in \Sigma$ ,  $q_2 \in Q$ , a set of clocks to be reset  $\lambda \subseteq X$ , and a guard  $\mu \in XC(X, P)$ .

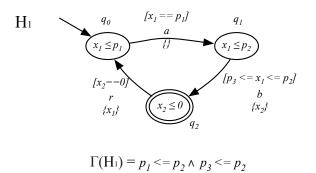

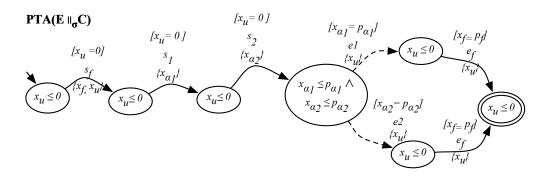

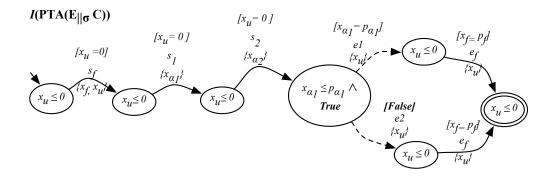

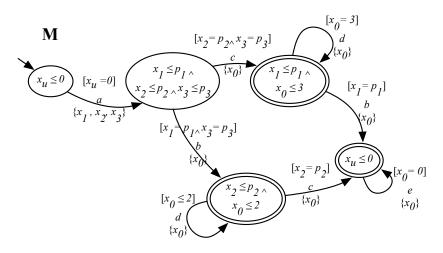

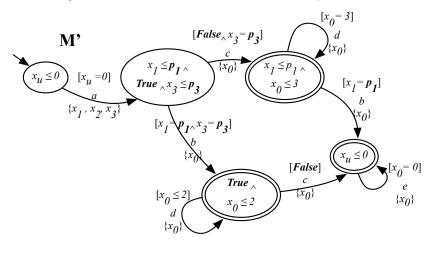

Figure 3.4: General examples of Parametric Timed Automata.  $\Gamma(H_1)$  describes the conditions that parameters  $\{p_1, p_2, p_3\}$  of  $H_1$  need to satisfy to reach a final state.

The parameters in PTA can be instantiated into constant real-values. This means that every time that a parameter p appears in a guard or an invariant, the parameter is replaced by a constant real value r. A parameter valuation  $\gamma$  for

a set of parameters P is function  $\gamma: P \to \mathbb{R}_{>0}$  that assigns to each parameter  $p \in P$  a constant real-value  $\gamma(p)$ . Given a parameter valuation  $\gamma$  and a PTA, we can obtain a TA by replacing the parameters with the constant real-values that are defined by  $\gamma$ . However, some parameter valuations might fix the guards and invariants with values that make impossible to take some transitions. For instance, if the invariant of the state becomes  $x_1 \leq 60$  and the guard of the only outgoing transition becomes  $x_1 \ge 100$ . In this case, the invariant and the guard will never be valid at the same time. Thus, it is not possible to continue progressing from that state. When many transitions become invalid, there might not be a path that reaches a final state from the initial state. Then, the TA obtained may become invalid as a whole, since it is not describing any accepted behaviour. Figure 3.4 shows a parametric timed automaton  $H_1$  that is similar to the timed automaton  $T_1$ but with some parameters instead of constant numbers in the conditions. In this example, if parameter  $p_3$  becomes 100, parameter  $p_2$  becomes 60 and parameter  $p_1$ becomes 10, the final state is not reachable. Thus, the parameters must satisfy certain conditions to reach a final state.

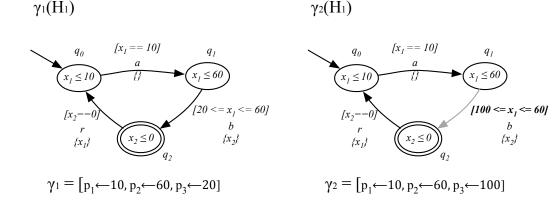

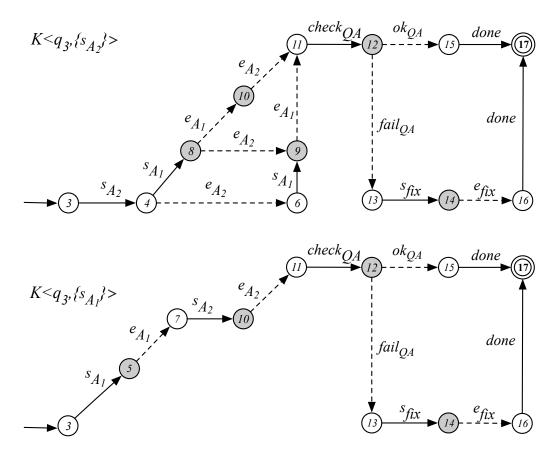

Figure 3.5: Timed automatons obtained by replacing the parameters of  $H_1$  with the values indicated in each parameter valuation.

The assignment of values to the parameters is formalised as a *parameter* valuation. A parameter valuation is consistent with a PTA, if there exists at least one path that reaches a final state in the TA obtained from replacing the parameters with the constant values. In other words, the TA obtained describes a

non-empty language. We denote a parameter valuation  $\gamma$ , i.e., an assignment of real values  $(r_1, \ldots, r_n) \in \mathbb{R}_{\geq 0}^{|P|}$  to the parameters  $(p_1, \ldots, p_n) \in P$ , that is consistent with a PTA H as  $\gamma \Vdash H$ , or simply  $(r_1, \ldots, r_n) \Vdash H$ . The set of parameter valuations that is consistent with a PTA H is denoted in the literature as  $\Gamma(H)$  [25].  $\Gamma(H)$  is a set of constraints that a parameter valuation must satisfy to produce a valid TA from a given PTA.  $\Gamma(H)$  can be expressed as a symbolic expression, which can be calculated by performing a fixed point iteration algorithm [26]. For instance, in the example of Figure 3.4,  $\Gamma(H_1)$  is defined as  $\Gamma(H_1) = p_1 \leq p_2 \wedge p_3 \leq p_2$ . Also note that by applying the parameter valuation  $\gamma_1 = [p_1 \leftarrow 10, p_2 \leftarrow 60, p_3 \leftarrow 20]$ to  $H_1$  we obtain a timed automaton like  $T_1$  from Figure 3.3. We denote it as  $\gamma_1(H_1)$ . As mentioned above, given a valuation  $\gamma_2 = [p_1 \leftarrow 10, p_2 \leftarrow 60, p_3 \leftarrow 100]$ , we obtain a timed automaton  $\gamma_2(H_1)$ , in which there is no trace that reaches a final state. Figure 3.5 shows these two timed automaton. The transition shown in gray cannot be traversed because no clocks would satisfy that condition.

In general, computing  $\Gamma$  is undecidable, if there are more than three clocks in PTAs with cycles [25]. However, this work focuses on PTAs that do not have cycles, in which the symbolic procedure finishes [61]. In Chapter 7 we show the details to calculate  $\Gamma(H)$  for the type of PTAs involved in this work.

#### 3.6 Satisfiability modulo theories

The Boolean satisfiability problem (SAT) [62] is the problem of determining if a propositional boolean formula can be satisfiable or not. That is, to find an assignment of values (True or False) to the propositions of the formula that makes the formula be True. If such assignment exists, then the formula is satisfiable. For instance, the formula  $p \lor q$  is satisfiable because the assignment p = Trueand q = False makes  $p \lor q = True$ . However, the formula  $p \land \neg p$  is unsatisfiable because there is no possible assignment that makes this formula evaluate to True.

In the same vein, the satisfiability modulo theories (SMT) [27] problem is a decision problem for logical formulas of theories expressed in first order logic with equality. SMT formulas are more expressive than the ones of SAT. Among the supported theories are the theory of integers, the theory of real numbers, the theory of lists, the theory of arrays and theories of many other data structures. In

this work, we use SMT for solving decidability problems of the theory of real numbers. For instance, the formula  $p_1 > p_2 \land p_1 \ge 0 \land p_2 \ge 0$  is satisfiable because there exists at least a pair of values  $p_1 = 60$  and  $p_2 = 20$  that evaluates the formula to *True*. This are the type of formulas (or expressions) that are produced by  $\Gamma$ . Checking whether these expressions are satisfiable or not is central to our approach.

## 4 Industrial Automation Example

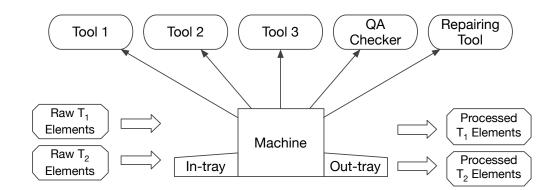

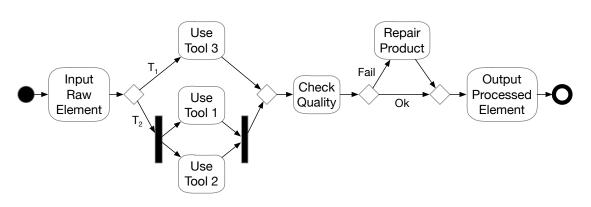

Assume an industrial automation setting, in which different product types are to be produced through a variety of processing activities according to given constraints. For simplicity, we assume that there are two product types. The machine has an inner tray where the raw elements of the products can be placed. The products have to be processed by using different tools that are available in the machine. Figure 4.1 shows a high level illustration of the configuration of the environment.

Figure 4.2 describes the list of requirements that the machine needs to satisfy to produce a product by using different tools. Some of the requirements are general, while others are specific to the product type to be processed.

According to the description from Figure 4.2, there are some tasks or activities that need to be performed to produce a product. First, the machine transforms the input-raw elements into processed elements by using some of the tools. Second, it checks that the processed elements fulfill the quality requirements by using a QA *Checker*. Third, if the quality of the product is not right, the machine repairs the products by using a *Repairing Tool*. Finally, it places the processed and quality

Figure 4.1: Illustration of an industrial automation plant with five tools and two types of input products to be processed.

General requirements:

- 1. Check the quality of a product before placing it in the output tray.

- 2. If the processed product does not pass the quality check, use the repairing tool to meet the quality requirements.

- 3. Emit a signal when the product is placed in the output tray.

- 4. Warning! Never start the tool 2 while the tool 1 is being used because it may produce a power outage.

- 5. Process one product at a time.

Product type specific requirements:

Type 1: Use the tool 3 to process them.

Type 2: Use the tool 1 and tool 2 to process them. The tools can be applied in any order.

Figure 4.2: Requirements of the industrial automation example in natural language.

assured elements into the out-tray. The machine can process one element at a time, and it needs to use different tools depending on the product type.

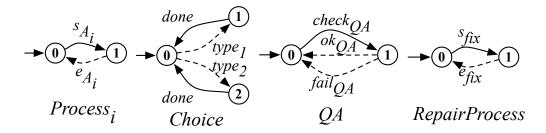

Figure 4.3 shows an illustration of the activities that have to be done to process a product. The restrictions about when the tools cannot be used at the same time are not shown in this diagram. According to the requirements, there are three

Figure 4.3: Diagram describing the activities that must be performed to process a product depending on the input type.

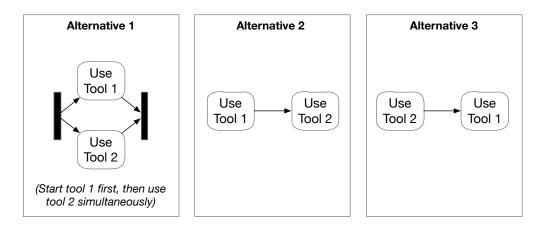

alternatives for using the tools on products of type 2, which are shown in Figure 4.4. All of these alternatives satisfy the requirements. However, *Alternative 1* seems to be preferable from a time perspective because it uses the tools simultaneously. This may save time in processing a product regardless the time it takes to use each of the tools. The main goal of this work is to find a way to express preference for solutions that may save execution time in a qualitative manner, i.e., without using numbers to represent the durations of the activities. We believe that it is possible to produce a comparison framework that can show that solutions like *Alternative 1* always have lower-makespan than *Alternative 2* or *Alternative 3*. Besides, we aim to produce synthesis algorithms that avoid sequential solutions like the ones show here, when concurrent alternatives are available.

Figure 4.4: Alternatives for using the tools on products of type two.

# 5 A Qualitative Approach for Makespan

In this chapter we define the proposed approach from a high level perspective. Section 5.1 presents the two main problems that we aim to solve and the role that activities play in them. Section 5.2 defines the concept of makespan in qualitative problems with safety and reachability goals. Section 5.3 defines how to measure and Section 5.4 how to compare makespan of controllers. Section 5.5 defines how to deal with contigencies when comparing makespan. Section 5.6 defines makespan-minimising controllers, which are the type of controllers that we would like to generate. Section 5.7 introduces the main idea of the proposed algorithm to obtain a makespan-minimising controller. The details will be described in the following chapters.

#### 5.1 The main parts of the problem

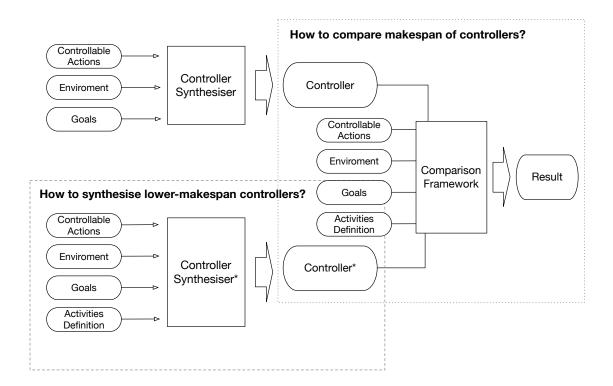

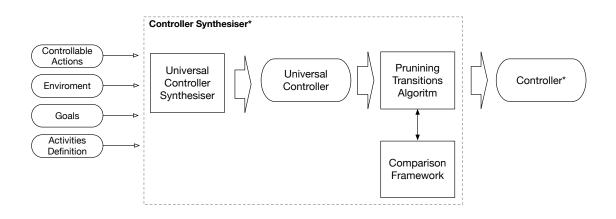

Our goal is to produce a framework to generate controllers that are preferable regarding a qualitative metric. The metric chosen in this work is makespan, which is explained in the next section. Thus, one of the problems we aim to solve is *How to synthesise lower-makespan controllers?*. Typically, the inputs of a control problem are a description of the environment, a set of system goals and the actions that can be controlled. The *Controller Synthesiser* from Figure 5.1 illustrates this case. We propose to add extra information to the control problem to define algorithms that use this information to give more preferable controllers regarding makespan. This is illustrated in the second *Controller Synthesiser*\* of the same figure. In this approach, we relieve the user from providing quantitative estimations, but require additional qualitative description of the environment. This description is the *activities definition*, which is simply a description of the activities are related in the environment. Details about activities are described in Section 5.3. In our approach, *Activities definition* must be specified at design time, because they are used to synthesise the controller.

Figure 5.1: Two main problems and its different components.

Activities definition play also an important role in the other part of the

problem, which is how to compare makespan of controllers? (qualitatively). The problem is to determine if any of the two controllers has lower-makespan than the other. This is also illustrated in Figure 5.1 as input of the comparison framework. Here activities are used to provide a timed semantics to controllers, which is defined as a parametric timed automata. By modelling activities, we can define a way to compare controllers qualitatively. Besides, activities are also used when defining schedulers, which are used to model different behaviour of the environment regarding contingencies. Details about this is described in Section 5.5.

#### 5.2 Defining makespan

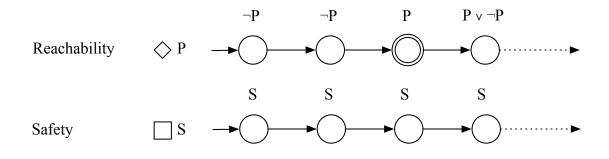

This research focuses on controllers with safety and reachability goals. Safety goals are used to define behaviour that should always be satisfied. It can be used to model bad behaviour that we want to avoid or to ensure some good behaviour throughout the whole execution. Reachability goals are typically used to model good behaviour that we want to achieve. Reachability goals can be seen as missions that must be accomplished. The satisfaction of the goals is evaluated when executing the controller with its environment. Figure 5.2 shows the satisfaction of these formulas over traces of the the  $E \parallel C$ . Note that a controller must continue ensuring the safety S proposition after reaching a state that makes the proposition P become True.

Figure 5.2: Satisfaction of safety  $(\Box S)$  and reachability  $(\Diamond P)$  goals over traces.

We define the *goal states* as those in which the reachability goal becomes accomplished, i.e., the mission is achieved. In Figure 5.2, the goal state is denoted

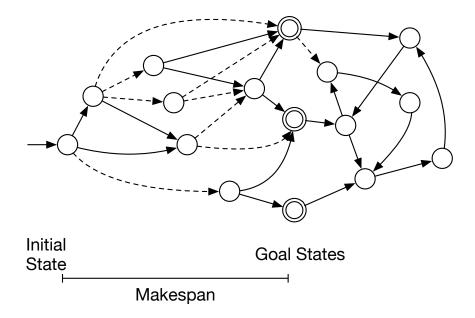

with double-lined circle. Achieving a reachability goal in the minimum time possible is a preference that is often desired. Thus, we define *makespan* as our metric to evaluate the quality of a controller. Makespan measures the time that elapses from the start of a task to the end. In our approach, makespan is measured from the initial state to the goal states. After reaching a goal state, a controller may do the minimum actions to keep itself safe, or it could continue to do other safe activities. The only condition after reaching a goal state is to respect the safety goals. This type of controllers is of interest in environments where a new mission can be assigned by updating the system with a new controller [17]. For example, a robot that is deployed in another planet and receives missions periodically. Figure 5.3 shows an abstract representation of how a safety and reachability controller would look like. In the following chapters, we will often illustrate the controllers only from initial state to goal states, because those are states considered when measuring makespan.

Figure 5.3: Abstract illustration of a controller for safety and reachability. Makespan is measured from the initial state to the goal states. Actions are omitted.

#### 5.3 Measuring makespan

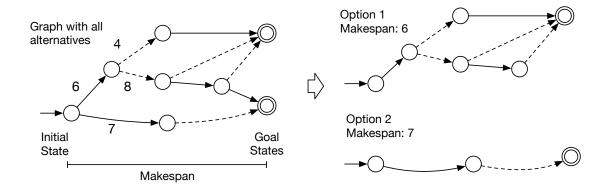

Makespan tends to be considered as a quantitate measure. Quantitative algorithms for makespan can produce optimal solutions when precise quantitative models are available. However, quantitative information are not always available or precise enough to be modelled. For instance, not always the duration of the activities are known in advance. In those cases, avoiding quantitative modelling may be desirable, because using quantitative algorithms on those models may produce solutions that are over-fitted to inaccurate numbers. For example, Figure 5.4 shows an abstract example of calculation of the average duration on a graph that has all the possible alternatives to reach goal states. A quantitative approach would choose a solution like *Option 1* because the value that represents makespan is lower than that of *Option 2*. However, if the estimation of those values were inaccurate we would be discarding the *Option 2* arbitrarily.

Figure 5.4: Illustrative example of using numbers to measure makespan. Numbers represent average duration to reach goal states. Actions are omitted.

In our approach, we define a qualitative way to compare controllers. This approach requires engineers to annotate the control problems with *activities definition*, which aggregate actions that are implicitly related. For instance, the action of *start doing something* and *finishing doing something* can be modelled as a *doing something* activity. This means that our method does not require estimating numbers that represent durations, but making the implicit relation between the actions become explicit as activities.

The way in which we measure makespan is similar to a logical description of the behaviour of the controllers regarding activities. For instance, the makespan of a controller is the time it takes the activity *doing something* plus that of activity *moving somewhere*. In more complex scenarios, the description would also have disjunctions depending on contingencies. For example, if the robot is in the right location the makespan of the controller is the time takes *doing something*, otherwise it is the time it takes *moving to location* plus that of *doing something*.

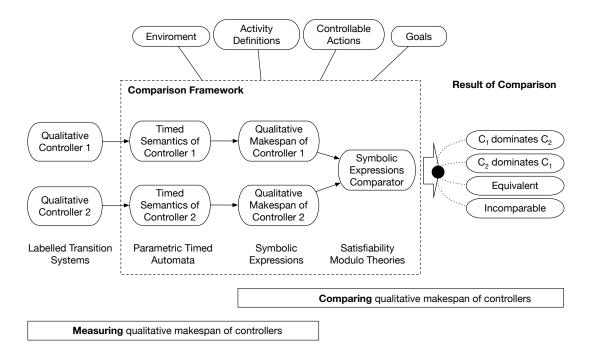

Figure 5.5: Formalisms that are used in each step of the transformation to solve the problem of measuring qualitative makespan and comparing it.

This is formalised by defining a timed semantics for LTS controllers with activities definition by using parametric timed automata. Activities are used to define symbols (clocks and parameters) of a PTA, which is the timed semantics of a controller. Then, we obtain a logical expression from the PTA, which is defined in terms of these symbols. This expression is the qualitative makespan of a controller based on activities definition. Figure 5.5 illustrates the process of this transformation. As we can observe in this figure, the next issue to address is how to compare qualitative makespan of two different controllers.

#### 5.4 Comparing makespan

Given a qualitative control problem, there are different solutions (or controllers) that can be obtained by using different synthesis algorithms. In a quantitative approach, it would be easy to compare them by using average-case or worst-case makespan. In our qualitative approach, we need to define how to compare qualitative makespan of controllers, because they are logical expressions with parameters that represent activities durations, for which it is not defined how to compare them. Our goal is to establish a comparison relation between these expressions. For instance, it seems that *doing something* takes longer than *moving to location* plus *doing something*, but we need to formally show that.

To establish the relation between the qualitative makespan of two controllers, we are going to perform two comparisons, we are going to check if one controller can have a behaviour of higher makespan than the other, and the reverse. In Figure 5.5 this is modelled by the *Symblic Expressions Comparator*. Checking for a behaviour of higher makespan means to find a case in which the controller performs worse than the other. After checking that in both directions, the defined comparison produces one out of the four possible results, which are also shown in the same figure:  $C_1$  dominates  $C_2$ ,  $C_2$  dominates  $C_1$ , equivalent or incomparable. A controller dominates the other, if it always behaves better or the same with the other. The details about how to measure and compare makespan are explained in Chapter 7.

#### 5.5 Dealing with contingencies

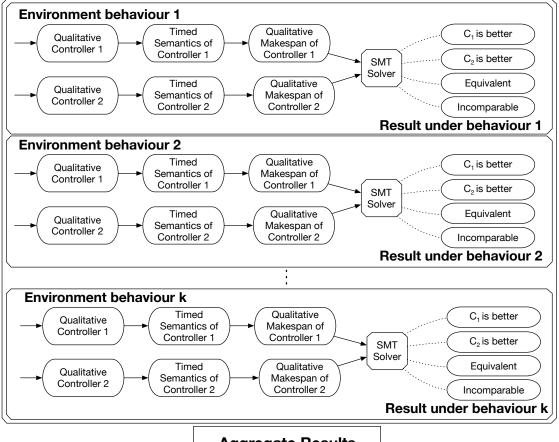

The problems that are considered in this work are reactive, which means that the behaviour of the environment is not always the same. The reactiveness of the environment is modelled with uncontrollable actions. The controller cannot choose which or when uncontrollable actions happen. Instead, the environment chooses during the execution of the controller. It would be unfair to compare controllers assuming different behaviour of the environment. Thus, the comparison defined here fixes the behaviour of the environment and then compares the controllers under the same conditions.

Aggregate Results

| C <sub>1</sub> dominates C <sub>2</sub> |                          |            |         |

|-----------------------------------------|--------------------------|------------|---------|

| C <sub>1</sub> is better                | C <sub>2</sub> is better | Equivalent | Incomp. |

| > 1                                     | 0                        | >= 0       | 0       |

| C <sub>2</sub> dominates C <sub>1</sub> |                          |            |         |

|-----------------------------------------|--------------------------|------------|---------|

| C <sub>1</sub> is better                | C <sub>2</sub> is better | Equivalent | Incomp. |